# HIGH SPEED RADIX-2 BUTTERFLY STRUCTURE USING NOVEL WALLACE MULTIPLER

Dissertation submitted in fulfillment of the requirements for the Degree of

# MASTERS OF TECHNOLOGY

# IN

# **ELECTRONICS AND COMMUNICATION**

By

# GARIMA THAKUR

Enrollment No.162005

Under the Supervision of

# **DR. SHRUTI JAIN**

AND

# **DR. HARSH SOHAL**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING JAYPEE UNIVERSITY OF INFORMATION TECHNOLOGY WAKNAGHAT, SOLAN -173234, INDIA MAY, 2018

# TABLE OF CONTENTS

| DECLARATION BY THE SCHOLARv   |

|-------------------------------|

| CERTIFICATEvi                 |

| ACKNOWLEDGEMENTvii            |

| ABSTRACTviii                  |

| LIST OF FIGURESx              |

| LIST OF TABLES xiii           |

| ABBREVIATIONSxiv              |

| CHAPTER 1 INTRODUCTION1       |

| 1.1 Adders1                   |

| 1.2 Multiplier                |

| 1.3 FFT                       |

| 1.4 Need for Low Power Design |

| 1.5 Programming Language      |

| 1.6 Research Approach7        |

| 1.7 Organization7             |

| 1.8 Tools Used                |

| CHAPTER 2 LITERATURE SURVEY9  |

| CHAPTER 3 ADDERS              |

| 3.1 Basic Adder               |

| 3.1.1 Half Adder              |

| 3.1.2 Full Adder14            |

| 3.2 Complex Adder15                                      |

|----------------------------------------------------------|

| 3.2.1 Ripple Carry Adder15                               |

| 3.2.2 Carry Select Adder16                               |

| 3.2.3 Carry Skip Adder17                                 |

| 3.2.4 Carry Look Ahead Adder18                           |

| 3.2.5 Kogge Stone Adder21                                |

| 3.3 Implementation of 4-bit Adders24                     |

| 3.4 Proposed Adder                                       |

| 3.5 Comparison Table                                     |

| 3.5 Conclusion                                           |

| CHAPTER 4 MULTIPLIERS                                    |

| 4.1 Different Multipliers                                |

| 4.1.1 Array Multiplier                                   |

| 4.1.2 Wallace Multiplier                                 |

| 4.1.3 Vedic Multiplier                                   |

| 4.2 Implementation of 4-bit Multiplier41                 |

| 4.3 Proposed Multiplier                                  |

| 4.4 Conclusion                                           |

| CHAPTER 5 FAST FOURIER TRANSFORMS                        |

| 5.1 Implementation of 16 and 32 bit efficient Adder      |

| 5.2 Implementation of 16 and 32 bit efficient Multiplier |

| 5.3 Transforms            |    |

|---------------------------|----|

| 5.3.1 Butterfly Structure | 61 |

| 5.4 Conclusion            | 63 |

| CONCLUSION                | 67 |

| REFERENCES                | 68 |

| PUBLICATION               | 71 |

### **DECLARATION BY THE SCHOLAR**

I hereby declare that the work reported in the Masters Of Technology thesis entitled "High Speed Radix-2 Butterfly Structure using Novel Wallace Multiplier" submitted at Jaypee University of Information Technology, Waknaghat India, is an authentic record of my work carried out under the supervision of Dr. Shruti Jain and Dr. Harsh Sohal. I have not submitted this work elsewhere for any other degree or diploma.

gasina Garima Thakur ECE Department

JUIT

Date: 10-65-2018

#### JAYPEE UNIVERSITY OF INFORMATION TECHNOLOGY

(Established by H.P. State Legislative vide Act No. 14 of 2002) P.O. Waknaghat, Teh. Kandaghat, Distt. Solan - 173234 (H.P.) INDIA Website: www.juit.ac.in Phone No. (91) 01792-257999 Fax: +91-01792-245362

#### CERTIFICATE

This is to certify that the work reported in the M.Tech project report entitled "High Speed Radix-2 Butterfly Structure using Novel Wallace Multiplier" which is being submitted by Garima Thakur in fulfillment for the award of Masters of Technology in Electronics and Communication Engineering by the Jaypee University of Information Technology, is the record of candidate's own work carried out by her under our supervision. This work is original and has not been submitted partially or fully anywhere else for any other degree or diploma.

Dr. Shruti Jain Associate Professor ECE Department JUIT Date: 10-05-18

Dr. Harsh Sohal Assistant Professor ECE Department JUIT Date: 10 - 05-2018

# ACKNOWLEDGEMENT

I might want to offer a profound feeling of gratitude and indebtedness to **Dr. Shruti Jain and Dr. Harsh Sohal**, Department of ECE and supervisor for this work, for their direction, support, inspiration, and consolation all through the finish of this work. Their excitement to listen to the issues, their educative remarks, their suggestions for the convenient and successful completion of this work has been exemplary.

We are appreciative to **Prof. Dr. Samir Dev Gupta**, Director and Head of Department of ECE for his superb support during our work. I might likewise want to thank all of the professors & other supporting members of the department of Electronics and Communication Engineering for their generous help in different courses for the finish of this work. Last however not the slightest, I might genuinely want to thanks, every one of my companions, Ph.D. researchers and friends for their insightful recommendations for fulfilling this undertaking.

# Garima Thakur

Date: 10-05-2018

# ABSTRACT

In any Central Processing Unit (CPU) the crucial components are Arithmetic and Logic Unit (ALU). ALU can perform different operation like addition, subtraction, multiplication etc. In this thesis addition and multiplication plays an important role because adders and multipliers are the basic building blocks of any Digital Signal Processing applications.

Firstly, in this work adder is used for addition of numbers but it also perform some arithmetic operations. In adders the basic buildings blocks are Half adder and Full adder because they are used for constructing complex adders like Ripple Carry Adder, Carry Select Adder etc. First analyzed efficient adder and used this efficient adder for implementation of modified Carry Increment adder. This modified adder used in many Signal Processing application and increases the speed of the circuit because nowadays delay optimization and power optimization become a very challenging problem with the increase of the portable devices.

Secondly, after adders the crucial component is multiplier. In multipliers the basic block for reducing partial product is adder. The efficient adder used in the multiplier for increasing the speed of circuit and used the circuit in an optimized way. For constructing an efficient multiplier different architecture are proposed so to design an efficient multiplier. A modified multiplier is proposed by using efficient multiplier with efficient adder so, to improve the overall performance of the circuit.

The goal of this is to analyze and compare various adders and multiplication schemes for highspeed and low power operations. Since the various Digital Signal Processing applications, require computationally efficient Multiply and Accumulate operations so the blocks with desired characteristics have to be chosen carefully. Various techniques have been proposed to design multipliers which are efficient in terms of performance, low power consumption and area.

Finally, the efficient adders and multipliers are used in FFT algorithm. FFT is used for signal processing applications. It consists of addition and multiplication operations, whose speed improvement will enhance the accuracy and performance of FFT computation for any applications. FFT are used to covert signal form time domain to frequency domain. In FFT

processing unit butterfly structure is the basic building block and are used for calculating the complex calculation. So, it is important to design an efficient adder and multiplier block and used this efficient block in butterfly structure.

Further work on Low Power Techniques on different multipliers needs to be done in order to make us choose a proper multiplier in accordance with the requirements by making the best possible trade off choice between Speed and Power in different circumstances.

# LIST OF FIGURES

| Figure 1.1  | Logical Circuit of Half Adder2                        |

|-------------|-------------------------------------------------------|

| Figure 1.2  | Logical Circuit of Full Adder2                        |

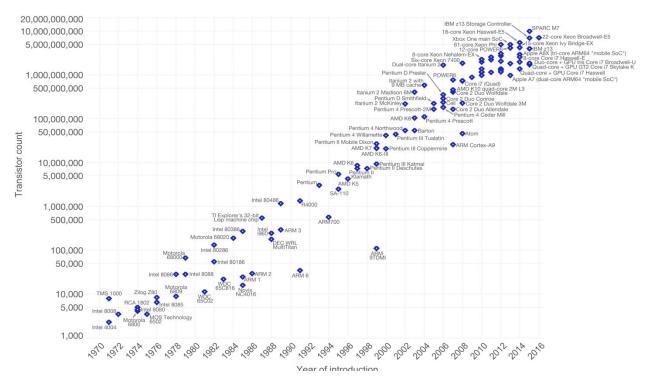

| Figure 1.3  | Number of transistors on IC (1971-2016)4              |

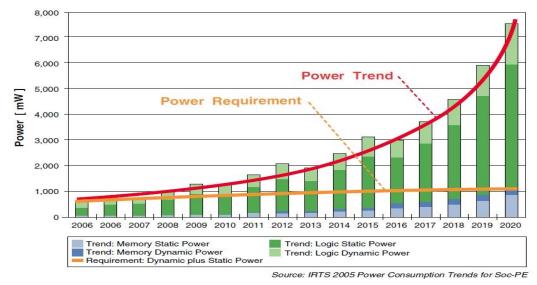

| Figure 1.4  | Power density trend versus power design requirements4 |

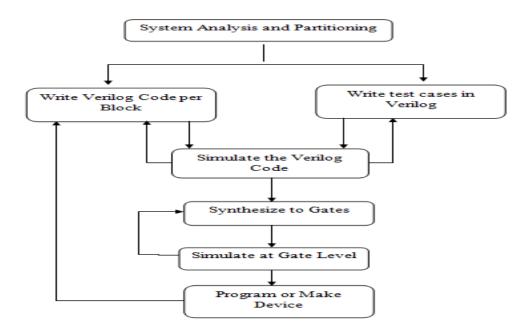

| Figure 1.5  | Design Flow using Verilog6                            |

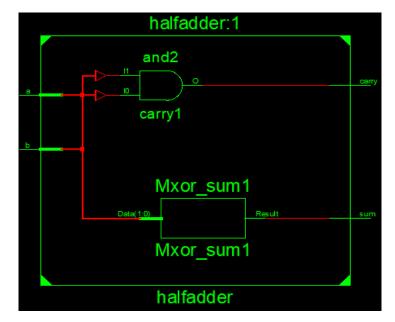

| Figure 3.1  | RTL Schematic of Half Adder                           |

| Figure 3.2  | RTL Schematic of Full Adder14                         |

| Figure 3.3  | 4 bit Ripple carry adder15                            |

| Figure 3.4  | RTL Schematic of Ripple carry adder15                 |

| Figure 3.5  | 4-bit Carry select adder16                            |

| Figure 3.6  | RTL Schematic of Carry select adder16                 |

| Figure 3.7  | 4-bit Carry skip adder17                              |

| Figure 3.8  | RTL Schematic of Carry skip adder                     |

| Figure 3.9  | 4-bit Weinberger-Smith CLA                            |

| Figure 3.10 | RTL Schematic of Carry Lookahead adder21              |

| Figure 3.11 | Block level diagram of a prefix adder22               |

| Figure 3.12 | 4-bit Kogge-Stone prefix adder                        |

| Figure 3.13 | RTL Schematic of Kogge stone adder23                  |

| Figure 3.14 | Representation of each KSA block                      |

| Figure 3.15 | Block diagram of CIA_RCA                                 |

|-------------|----------------------------------------------------------|

| Figure 3.16 | Block diagram of CIA_KSA28                               |

| Figure 3.17 | RTL Schematic of CIA_RCA                                 |

| Figure 3.18 | RTL Schematic of CIA_KSA                                 |

| Figure 4.1  | Block diagram of Multiplier architecture32               |

| Figure 4.2  | Partial product array for an M×N multiplier              |

| Figure 4.3  | 4×4 Array multiplier                                     |

| Figure 4.4  | RTL Schematic of 4 bit Array multiplier                  |

| Figure 4.5  | 8×8 partial product tree reduction of Wallace multiplier |

| Figure 4.6  | RTL Schematic of 4 bit Wallace multiplier                |

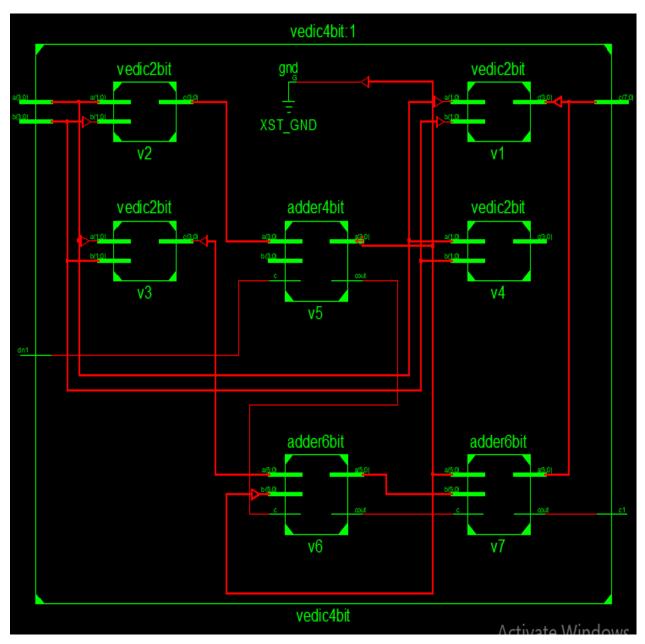

| Figure 4.7  | RTL Schematic of 4 bit Vedic multiplier,40               |

| Figure 4.8  | 8×8 Array multiplier architecture42                      |

| Figure 4.9  | 8×8 Vedic multiplier architecture                        |

| Figure 4.10 | 8×8 Wallace multiplier architecture                      |

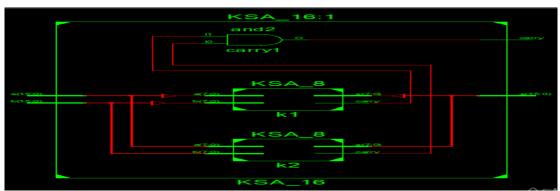

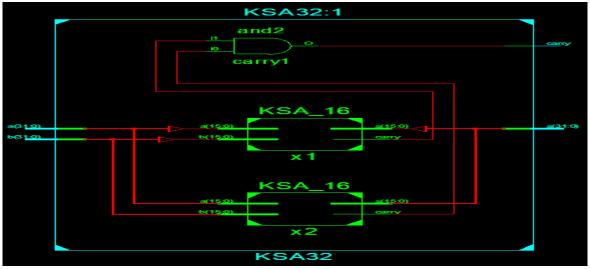

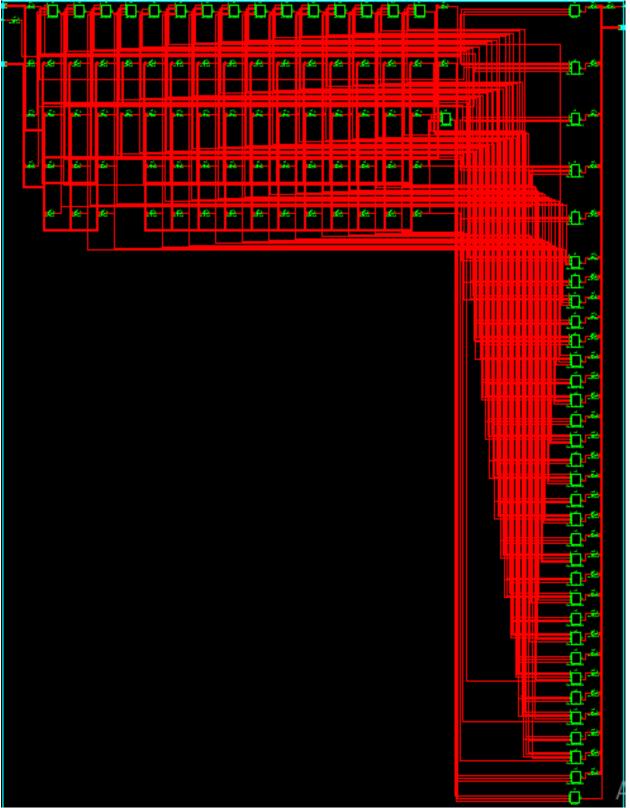

| Figure 5.1  | RTL Schematic of 16 bit KSA48                            |

| Figure 5.2  | RTL Schematic of 32 bit KSA49                            |

| Figure 5.3  | RTL Schematic of 16 bit CLA49                            |

| Figure 5.4  | RTL Schematic of 32 bit CLA                              |

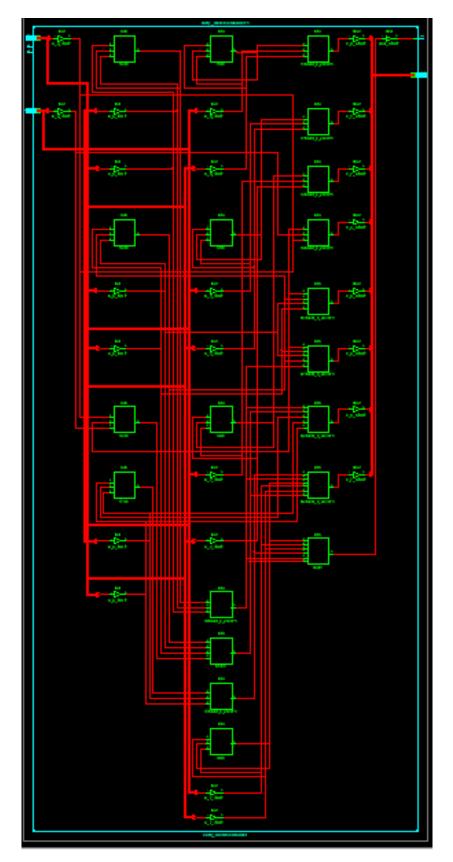

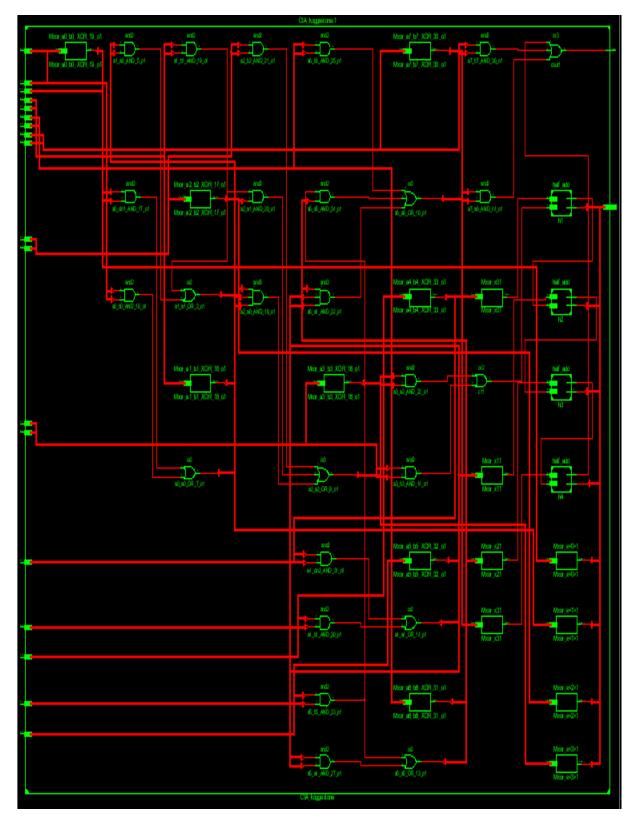

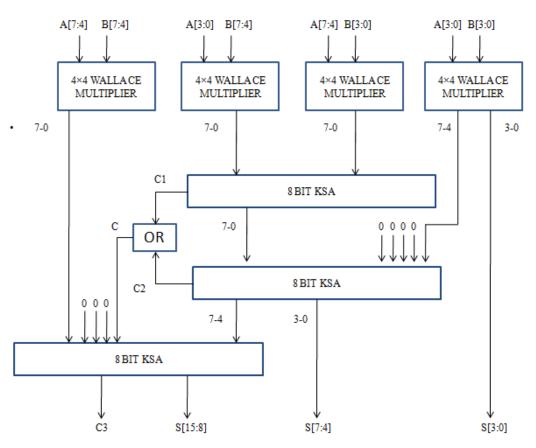

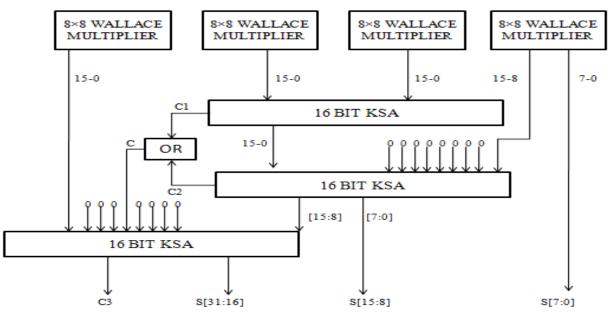

| Figure 5.5  | 16×16 Wallace multiplier Architecture using KSA53        |

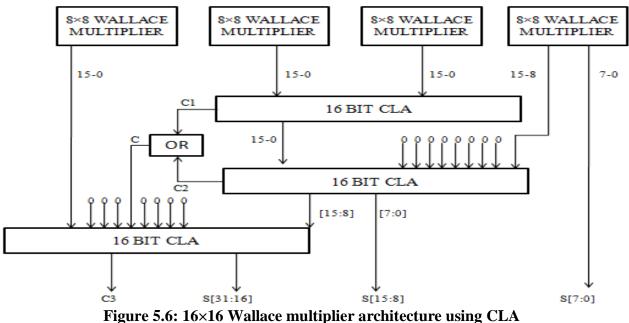

| Figure 5.6  | 16×16 Wallace multiplier Architecture using CLA          |

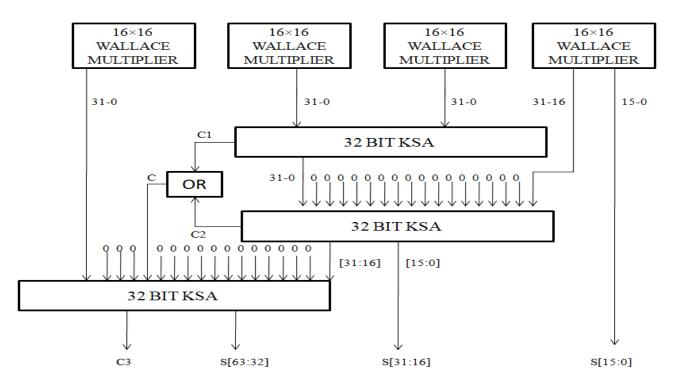

| Figure 5.7  | 32×32 Wallace multiplier Architecture using KSA          |

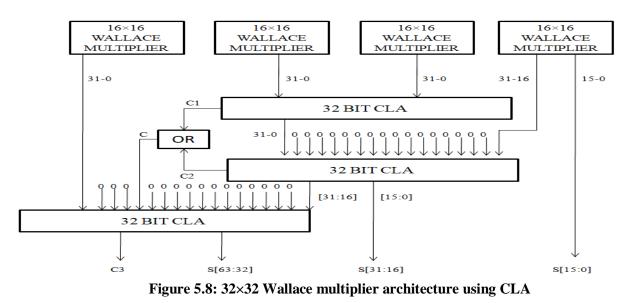

| Figure 5.8  | 32×32 Wallace multiplier Architecture using CLA | 56 |

|-------------|-------------------------------------------------|----|

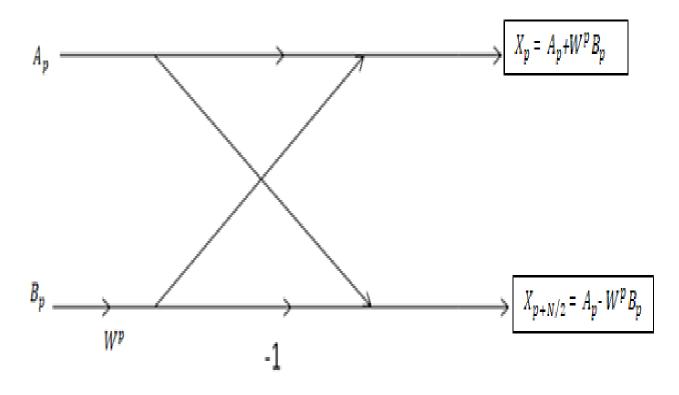

| Figure 5.9  | Butterfly Structure                             | 59 |

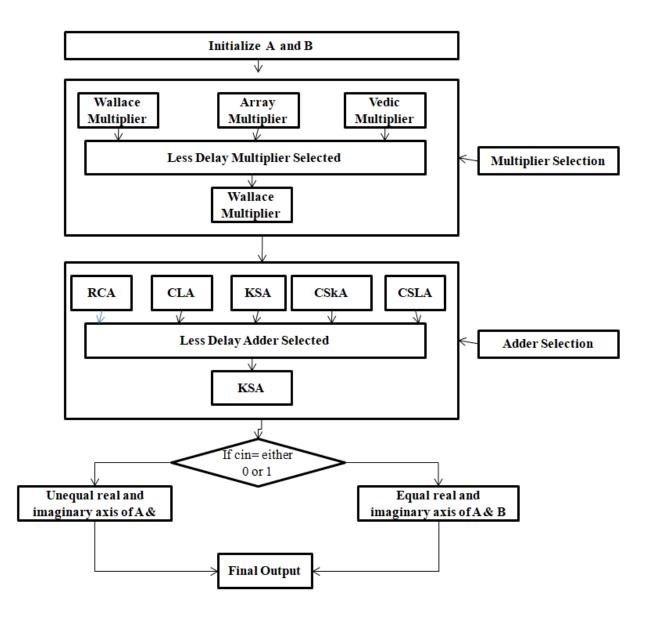

| Figure 5.10 | Flow diagram of Butterfly6                      | 51 |

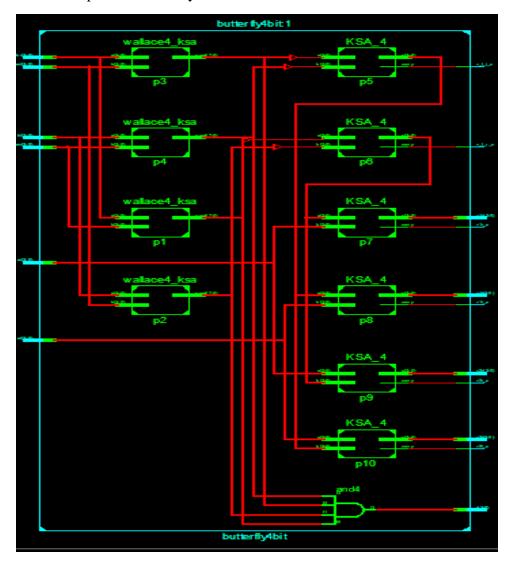

| Figure 5.11 | RTL Schematic of 4 bit butterfly                | 52 |

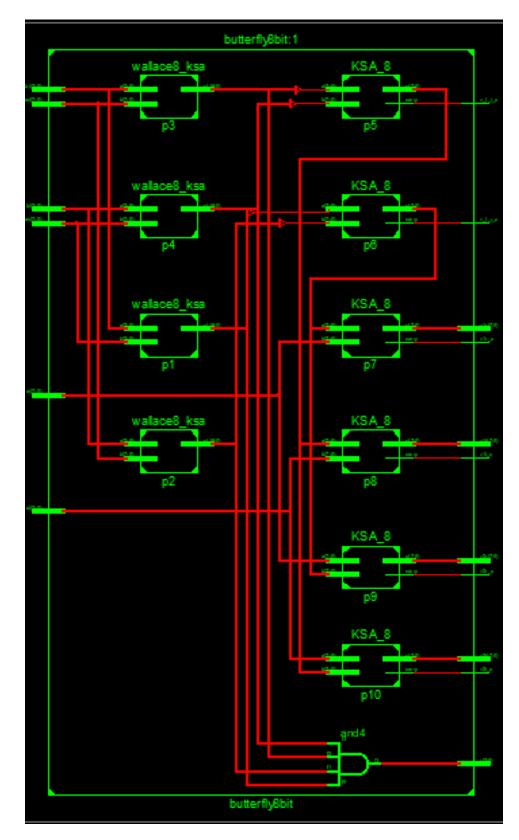

| Figure 5.12 | RTL Schematic of 8 bit butterfly                | 53 |

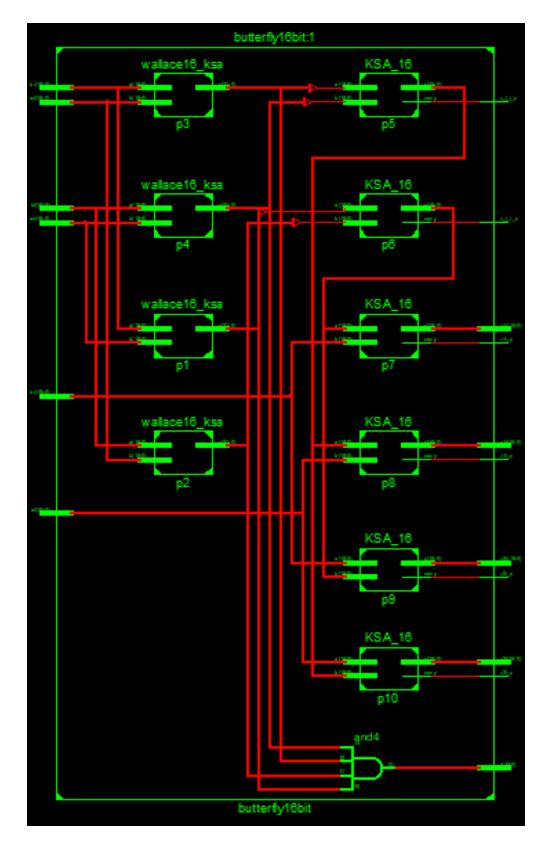

| Figure 5.13 | RTL Schematic of 16 bit butterfly               | 64 |

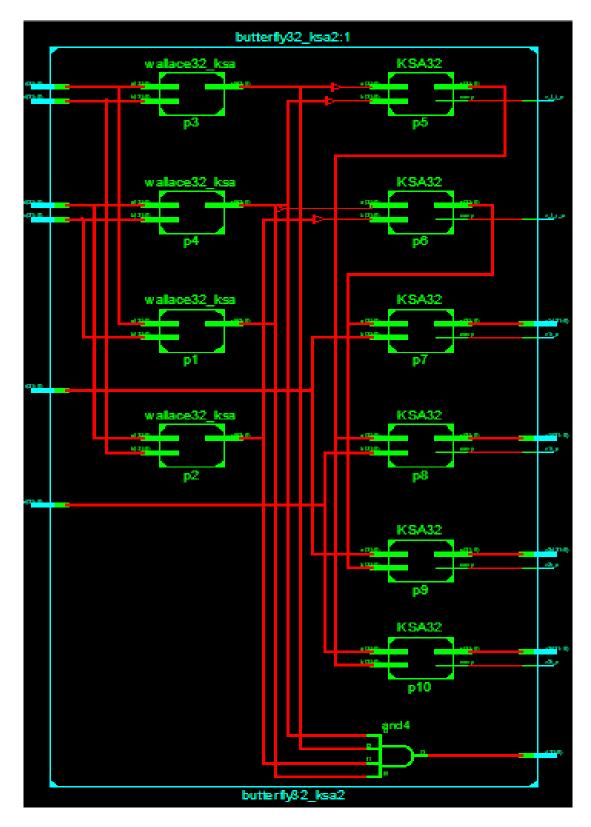

| Figure 5.14 | RTL Schematic of 32 bit butterfly               | 65 |

# LIST OF TABLES

| Table 3.1 Implementation Table of Full Adder                                                  |

|-----------------------------------------------------------------------------------------------|

| Table 3.2 Truth Table of Full Adder    19                                                     |

| Table 3.3 Area, Delay and Power calculation of 4-bit Adders                                   |

| Table 3.4 Area, Delay and Power calculation of 8-bit CIA                                      |

| Table 3.5 Comparison Table of Area, Delay and Power calculation of 8-bit CIA31                |

| Table 4.1 Area, Delay and Power calculation of 4-bit Multipliers41                            |

| Table 4.2 Area, Delay and Power calculation of 8-bit Multipliers45                            |

| Table 4.3 Comparison Table of Area, Delay and Power calculation of 8-bit Wallace multiplier45 |

| Table 4.4 Comparison Table of Area, Delay and Power calculation of 8-bit Vedic multiplier46   |

| Table 4.5 Comparison Table of Area, Delay and Power calculation of 8-bit Array multiplier46   |

| Table 5.1 Area, Delay and Power calculation of 16 bit Adder                                   |

| Table 5.2 Area, Delay and Power calculation of 32 bit Adder                                   |

| Table 5.3 Area, Delay and Power calculation of 16 bit Wallace multiplier                      |

| Table 5.4 Area, Delay and Power calculation of 32 bit Wallace multiplier                      |

| Table 5.5 Area, Delay and Power calculation of Butterfly structure                            |

# **ABBREVIATIONS**

- VLSI Very Large Scale Integration

- HDL Hardware Description Language

- VHDL Very High Speed Integrated Circuit Hardware Description Language

- ICs Integrated Circuits

- RCA Ripple Carry Adder

- CSA Carry Save Adder

- SQRT Square Root

- CSLA Carry Select Adder

- BEC Binary To Excess Code

- XOR Exclusive OR

- CBL Common Boolean Logic

- KSA Kogge Stone Adder

- DFR Design Of Reconfigurability

- CLA Carry Look Ahead Adder

- DSP Digital Signal Processor

- HA Half Adder

- FA Full Adder

- CSkA Carry Skip Adder

- LUT Look-Up Tables

- CLBs Configurable Logic Block

- SRAM Static Random Access Memory

- RAM Random Access Memory

- FPGA Field Programmable Gate Array

- IOB Input/Output Block

- CIA Carry Increment Adder

- WAP Write a Programme

- DFT- Discrete Fourier Transform

- IDFT- Inverse Discrete Fourier Transform

- FFT- Fast Fourier Transform

# CHAPTER 1 INTRODUCTION

Fast Fourier Transform (FFT) plays a crucial role in many Digital Signal Processing (DSP) applications. In communication systems like Orthogonal Frequency Division Multiplexing (OFDM), FFT is the most important block. It is used to convert a signal from time domain to frequency domain. In various systems there are requirements of high performance FFT to fulfill the demands of next generation with low cost and high speed. There is a need to design an efficient butterfly because it plays an important role in FFT processor. Nowadays, delay and power optimization have become a very challenging problem and portable electronic products are of great demand which need more backup, less area and less weight. So, low power circuit is designed because it directly affects the performance of the circuit. In general purpose processors the most important arithmetic units are adders and multipliers. The emphasis of our work is on minimizing the latency, with the goal being the implementation of the fastest multiplication blocks as possible. When we use digital system on a VLSI chip, much better Signal Processing Systems are implemented with the growth in the scale of integration. A large amount of energy and computation capacity is consumed in the signal processing. Architecture of arithmetic units is chosen carefully to reduce the power consumption and area. Arithmetic unit consists of Adders and Multipliers which are as follows:

#### 1.1 Adders

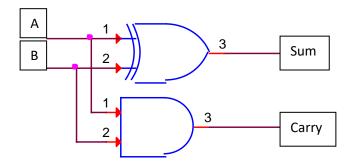

In digital IC designs the most frequent and essential operation is addition. Addition is done by adders and adders are the most important arithmetic units of any Digital Processing System. The most commonly used blocks in adders are Half Adder (HA) and Full Adder (FA) as shown in Figure 1.1 and 1.2. By using HA and FA many complex adder architectures are constructed. In this report many complex adders are implemented in terms of speed and power. The adder which has high speed is used for implementation of proposed design of adder. Adders are the basic building blocks of many applications. Adders are also used for calculate addresses, table indices and many more.

Figure 1.1: Logical circuit of Half Adder

Figure 1.2: Logical circuit of Full Adder

#### **1.2 Multipliers**

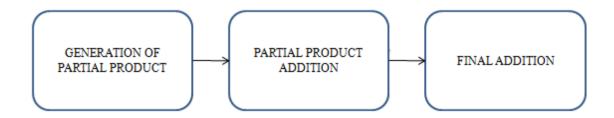

Multipliers also play a crucial role in the implementation of high performance circuits. These high performance circuits are used in many Digital Signal Processing applications, so there is a need to design an efficient multiplier to meet the requirement of the designer. For designing an efficient multiplier various characteristics are of taken care like: Speed-At high speed multiplier should perform operation, Accuracy- Correct result should given by good multiplier, Area- Less number of LUTs and Slices are occupied by multiplier and Power- The power consumed by the multiplier is less. Adders are used for addition of partial products of efficient multipliers. Three steps are followed for multiplication process: firstly, generation of partial products, second addition of partial products and finally, final addition. In this work the proposed multiplier is implemented using the adder with high speed and low power so to design an efficient multiplier. This efficient multiplier is used in many applications such as Image Processing, DSP, microprocessors etc.

#### **1.3 FFT**

In Discrete Fourier Transform (DFT) and Inverse Discrete Fourier Transform (IDFT) the complex numbers of arithmetic operations like addition and multiplication are required. For implementation of DFT one of the most efficient ways is FFT because it reduces the usage of arithmetic units. Arithmetic operations of DFT has O(N×N) order and FFT has O(N log N) order. Basically, FFT is used to covert signal to frequency domain from time domain. Nowadays, in Wireless Communication researchers employed FFT processor so, to achieve low power, high speed and low area utilization. For N-point data sequence the DFT is shown in Equation 1.1.

$$X[k] = \sum_{n=0}^{N-1} x[n] W_N^{kn}$$

(1.1)

For N-point data sequence the IDFT is shown in Equation 1.2.

$$X[n] = \frac{1}{N} \sum_{k=0}^{N-1} X[k] W_N^{-kn}$$

(1.2)

Where  $W_N^{kn} = e^{-j\frac{2\Pi}{N}kn}$

In FFT the most important block used is butterfly block because for increase the performance of the FFT processor firstly, it is important to design the high speed and low power consumption butterfly element. Butterfly is implemented using an efficient multiplier and adder. Different adders and multipliers circuits are designed, implemented and compared as explained in Chapter 2 and Chapter 3. Later proposed adders and multipliers are compared with the existing work.

#### **1.4 Need for Low Power Design**

During the last decades there is an increase in the integrated circuits which is predicted by Moore's Law. Figure 1.3 shows that every two year the number of transistors in IC doubles. As the feature size decreases there is reduction of power consumption. But as shown in Figure 1.3 power consumption increases with increase in the transistor count. Low power consumption in portable application is the major constraint. Power consumption and energy efficiency contribute to so many factors like longer operation time, higher workload etc in these situation power consumption become more critical. Reliability is also reduced as increase in on chip temperature due to increase in power consumption. Many problems are raised as power supply is delivered to chip such as noise immunity, power rails design etc. In many high performance applications the cost of cooling and packaging is increasing, so, power reduction is the primary objective of the designers in these applications.

Figure 1.3: Number of transistors on IC (1971-2016)[35]

Therefore, it is important to reduce power technique for current and future integrated circuit. Figure 1.4 shows the graph between power density and power density requirement for modern SoCs. The widening gap is shown in Figure 1.4 which shows the huge challenge for the designers that they face today. Lots of efforts are required for managing power in the design and the effort required is increasing with the new designs to meet new challenges.

Figure 1.4: Power density trend versus power design requirements[36]

As shown in Figure 1.3 increasing level of device integration and the complexity of the circuits is also increases. So, the primary goal is reduction of the power consumption. As the years goes by, the power dissipation also goes on increasing linearly and because of ever-shrinking size of chips the power density increases exponentially. If the rise of power density exponential then few years later a microprocessor designed who has power equal to nuclear reactor. So, this introduces reliability concerns as rise in power density such as thermal stresses, device degradation induced in hot carrier and it will result in loss of performance. As the increase in the demand of portable devices which is powered by batteries need low power chips this is the another factor.

#### **1.4 Programming Language**

Hardware Description Language (HDL) e.g. Verilog, VHDL are used to Write a Program (WAP). We have used Verilog programming for implementation of our digital circuit, because by using a HDL we can describe any digital hardware at any level. For design and verification of digital circuits it is most commonly used at the Register-Transfer Level (RTL) of abstraction Verilog language have many advantages over VHDL i.e. compact language, reduction operator etc. The Figure 1.5 summarizes the high level design flow for an ASIC (i.e. gate array, standard cell) or FPGA. Various steps are used for simulation and these steps are further divided into various other parts:

#### a) System-Level Verification

In system level verification there is complete verification of system model and simulates aspects. There is a detailed description of the system functionality and alternatively, maybe there is partial description of the system properties. For system-level modeling Verilog is not suited ideally.

#### b) **RTL Design and Test Bench Creation**

In RTL design the architecture of the system is stable and it's partitioning. In Verilog the RTL and test cases start capturing. Both the tasks are complementary and for various designs different RTL and test cases captured. If automated synthesis of logic is used then the RTL Verilog should be synthesizable. A disciplined approach is followed by test case.

In comparison to gate level simulation the RTL magnitude simulation is faster of one or two order and this shows that by spending more time in simulation it speed-up is best when more simulation is done. Against the specification the validation of functionality is done by RTL Verilog.

#### d) Look-Ahead Synthesis

In this synthesis design process will be done early, so the designers evaluate speed and area accurately and researchers check how the Verilog synthesis will be done, until the completion of functional simulation the production of main synthesis run. If the validation of design functionality is not done it is pointless to invest efforts and time in synthesis.

#### e) System Level

Verilog is addressed by system Verilog because it is not suited ideally for simulation at system level. VHDL is user-defined types in which designer allowed to work in the domain of problem. But Verilog is a pre-defined type in which designer allowed to work for scholastic simulation and build-in language features allowed for queuing, modeling performance and throughput.

**Figure 1.5: Design Flow using Verilog**

#### **1.3 Research Approach**

The basic idea behind our work is to design as efficient Butterfly Structure having low power and less delay because in FFT processor the basic block is Butterfly. We need to design efficient Butterfly block so it will the processor for fast computation in many application. In Butterfly the important block are adders and multipliers. An efficient multiplier block is implemented in which basic building block is adder. Nowadays, power optimization and delay optimization have become a very challenging problem. Firstly, our focus is on designing and implementation of adder in which we have examined different adders. The best adder is one with a minimum delay, low power consumption and finds a proper relation between LUTs, slices, power and delay. Secondly, best high speed adder is used for designing an efficient multiplier. Different multipliers are studied, designed and implemented using Verilog HDL. After getting all the results we find out the best multiplier with high speed and low power consumption. Finally, this efficient multiplier and high speed adder is used for the implementation of Butterfly Structure. Our future work is dedicated for reduction of more power consumption by reducing number of logic gates.

#### **1.4 Organization**

**CHAPTER 2:** LITERATURE SURVEY – This chapter explain the various types of algorithm used in adders and multiplier to design optimized circuit. The algorithm which is best suited to design high performance circuit is used.

**CHAPTER 3:** ADDERS – This chapter explains the different types of adders and there implementation. An optimized adder is used to design the high speed circuit.

**CHAPTER 4:** MULTIPLIERS – This chapter explains different types of multipliers there implementation and results. An optimized adders and multiplier combine to construct high speed circuit.

**CHAPTER 5:** FFT – This chapter explains the implementation of butterfly using efficient multipliers and adders. Butterfly plays crucial role in the processors.

7

# **1.5 Tools Used**

### Simulation Software:

• Xilinx 14.1 ISE design suite

### **Power Calculation**

• XPower Analyzer

### **CHAPTER 2**

### LITERATURE SURVEY

We have studied a lot of papers some are listed :

Akhter S. *et al.* 2017[1] in this paper various digital adders are used for comparative analysis of Vedic multiplier. Using CBL adder the 8-bit Vedic multiplier is 20% faster than BEC and is approximately 5% faster in terms of delay than RCA-CSA, SQRT-CSA and RCA. With the increase in the width size they have calculated outcome in terms of speed, area and leakage power.

Gowreesrinivas K. V. *et al.* 2016[2] in this paper using different types adders and by incorporating Vedic multiplier, a new type of multiplier is developed. The new developed multiplier i.e. Single Precision Floating Point(SPFP) have drawback of optimization of speed and area. By reducing interconnections and complexity the overall performance can be improved. It is observed that using combination of prefix sklansky adder and Vedic multiplier(VM) is best in comparison to other multipliers because it is best in terms of speed and complexity.

Gokhale G. R. *et al.* 2015[3] V M is implemented in this paper by means of lesser number gates, area, which is required by proposed CSLA. The Booth multiplier has more area, low speed compare to proposed V M, so it is superior. In the architecture of Vedic multiplier the addition block plays a important role for increasing and decreasing the performance of the circuit.

Murugeswari S. *et al.* 2014[4] in this a low power and an area efficient modified Wallace and truncated multiplier is implemented by using full adder which is based on mux. In the end it is concluded that reduction in area of modified truncated multiplier shows improvement in device utilization compared to modified Wallace multiplier.

Anjana R. *et al.* 2014[5] in this paper they designed a modified novel high speed multiplier as a result of combining Kogge stone adder with the multiplier to design the fastest multiplier.

S. Rajaram *et al.* 2011[6] in this paper proposed multiplier has less delay than the conventional multiplier. Proposed multiplier is Wallace multiplier which used Parallel prefix adder at the final stage, so there is improvement in multiplier.

R. B. S. Kesava *et al.* 2016[7] in this paper a simple approach is proposed for Wallace multiplier(WM) using Carry select adder(CSLA), so to reduce area. They implement CSLA with BEC in Wallace tree multiplier to occupying less power, less area and memory when compared to WM using CSLA and WM.

S.Srikanth *et al.* 2016 [8] in this paper by using multiplexers and XOR gate, proposed a full adder. In Wallace tree multiplier, by putting the proposed full adder in the decrease stage an average delay, power and area reduction achieved compared to existing method respectively is achieved.

D. Paradhasaradhi *et al.* 2014[9] an area efficient proposed WM is implemented in this paper by using CBL which is based on SQRT (square root) CSLA. There is reduction of delay and area by reducing the number of gates. Copying of adder cells are removed in the usual CSLA by sharing CBL term.

Gurjar P. *et al.* 2011[10] simulated and synthesized the different adders. The parameters like area and speed and the usefulness of fast adders is analyzed by simulated results. In the end, for 8-bit and 16-bit adders the caught parameters are analyzed. This paper infers that in conditions of delay and area consumption the Carry skip adder the efficient adder.

Bais K. *et al* 2016 [11] mentioned relationship of speed and area of different adders for various number of bits. From the delay comparison of adders, it is clear that Kogge Stone adder (KSA) is the fastest adder because it is parallel prefix adder. In the end they drive a conclusion that the speed and area cannot be optimized at the same time. If one parameter is improved the other

definitely shows degradation. In this paper we understand that KSA was the best when considered for delay but for area, as the number of bits of operands increases KSA occupies more area due to increase in parallel prefix stage.

Nandini M. *et al* 2015[12] discussed different kinds of prefix adders particularly Spanning adder, Sparse Kogge stone adder, Ladne fischer adder, Brent Kung adder and KSA. Correct practicality of every individual module was tested. This paper has resulted in reduced delay and power in the development of adders design. After analysis calculated KSA and Sparse KSA different parameters is being compared with the other adder. After the comparison less combinational delay of Kogge Stone adder with 12.499ns and less amount of power consumption of Ladner fischer adder with 0.26089 mW. In future using parallel prefix adders all the proposed architectures are designed.

Kulkarni R. *et al* 2015[13], discussed the performance of different adders. Characterization of different adders and implementation on an FPGA is done. Later than observe the outcome of comparisons, for two 8 bit addition numbers, CLA is superior. For three and four 8 bit numbers addition Carry save adder(CSA) with last stage built by RCA is preferable. In future work, low area as well as delay is required to design unique adder and to meet the requirement of current industry.

Mitre A. *et al* 2015[14], this paper compared completely different addition rule for various performance parameters i.e. power, area and speed for different adders such as Ripple carry adder(RCA), CSA, Carry select adder, Carry look ahead adder(CLA) and KSA. By merging Kogge stone and Carry select algorithms a high speed adder is then designed and works significantly faster than the rest.

Kumar A. *et al* 2013[15] explained that Ripple carry adder design is basic and it is appropriate for just addition of less width operand since delay run straightly with the width of operand. Linear area required by Carry skip adder which is not really bigger than area required by the RCA. As compare to other the delay of CLA is less and much faster than RCA. For high speed multiplication and accumulation, they can use Carry-look ahead adder(CLA) for 32 bit multiplier-accumulator unit. In fact the speed of multiplier has approximately twice the speed with carry-look ahead adder.

SaiKumar M. *et al* 2013[16], in this paper, presentation parameters of adders such as delay, area are compare, determined and design of various adders are discussed. Better performance in terms of area and delay is achieved through Carry increment adder (CIA) in comparison to additional adder topologies. For the later use, design of unique adder is needed which will provide small area, speed and meet up the requirements of current VLSI industry.

Suba C. *et al* 2014[17], design for reconfigurability (DFR) technique is presented by this paper for CLA.DFR proposal which has planned to isolate an extensive CLA keen on different little part ones. A small amount of area and delay penalty is incurred by the DFR scheme. The CLA has the smallest amount delay-area result. It is proper for conditions where together low power and fastness application. It is not feasible to apply CLA in steady delay for the wider-bit adders as there will be low speed, larger power consumption and substantial loading capacitance.

Singh A. K. *et al* 2017[28], in this paper, for higher radix FFT an efficient algorithm of butterfly unit was implemented. Taking various issues of FFT implementation an capable Butterfly block is implemented firstly and used this Butterfly block in FFT. Vedic multiplication result analyses in terms of slices and LUTs and implement an efficient butterfly in comparison to Booth multiplication (BM) technique. The design using CLA require large amount of hardware but faster than using RCA.

Rashmi M. J. *et al* 2014[29], in this paper, two algorithms are implemented which was based on DIT-FFT. First, algorithm was on the bases of Radix-2 FFT and second on the bases of Split Radix FFT. Both algorithms are compared for device utilization, speed and taking width size of 16 bits. Large amount of memory usage and increase in the delay as increases the single length of the proposed architecture using radix-2 FFT. This drawback was overcome by Split Radix FFT algorithm.

# CHAPTER 3 ADDERS

In digital IC designs the most frequent and essential operation is addition. Addition is done by adders and adders are the most important arithmetic units of any Digital Processing System. The most commonly used blocks in adders are HA and FA. By using HA and FA many complex adder architecture are implemented.

#### 3.1 Basic Adder

There are two types of basic adder which are used i.e. Half Adder and Full adder. These adders are the most important building block of any circuit.

**3.1.1 Half Adder (HA) :** HA is used for addition of two 1 bit number, which give sum bit(s) and carry bit (c). Sum bit is given by XORing A and B, Carry bit is given by ANDing A and B which is expressed by Equation 3.1 and 3.2 respectively.

$$Sum(s) = A XOR B$$

(3.1)

$$Carry(c) = A AND B$$

(3.2)

Figure 3.1: RTL Schematic of Half Adder

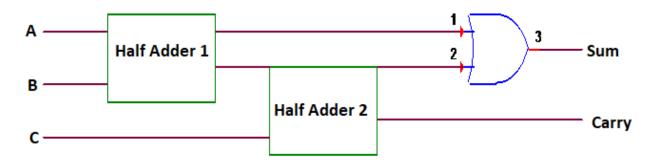

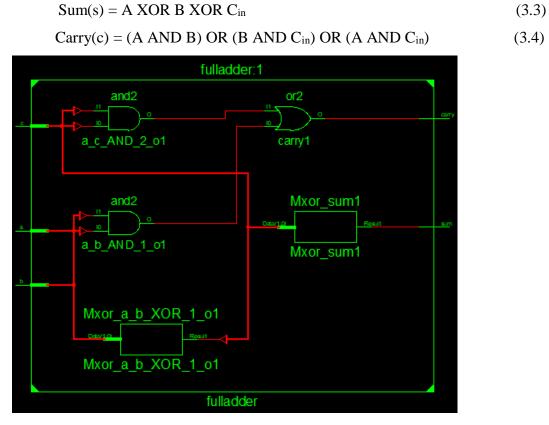

**3.1.2 Full adder (FA) :** FA adds three 1 bit number, which produces sum bit(s) and carry (c). By cascading two half adder it also produce sum and carry bit. Sum and Carry bit is expressed by Equation 3.3 and 3.4 respectively.

Figure 3.2: RTL Schematic of Full Adder

| Inputs |   | Half Adder1 O/P |    | Half Adder1 O/P |    | Final Output |   |      |

|--------|---|-----------------|----|-----------------|----|--------------|---|------|

| Α      | В | Cin             | S1 | C1              | S2 | C2           | S | Cout |

| 0      | 0 | 0               | 0  | 0               | 0  | 0            | 0 | 0    |

| 0      | 0 | 1               | 0  | 0               | 1  | 0            | 1 | 0    |

| 0      | 1 | 0               | 1  | 0               | 1  | 0            | 1 | 0    |

| 0      | 1 | 1               | 1  | 0               | 0  | 1            | 0 | 1    |

| 1      | 0 | 0               | 1  | 0               | 1  | 0            | 1 | 0    |

| 1      | 0 | 1               | 1  | 0               | 0  | 1            | 0 | 1    |

| 1      | 1 | 0               | 0  | 1               | 0  | 0            | 0 | 1    |

| 1      | 1 | 1               | 0  | 1               | 1  | 0            | 1 | 1    |

Table 3.1: Implementation Table of Full Adder

### 3.2 Complex Adder

Complex Adder are constructed by using basic adders i.e. HA and FA. Design circuitry of these adders is complex because they take number of blocks to design a circuit.

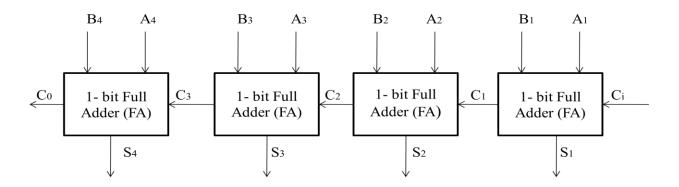

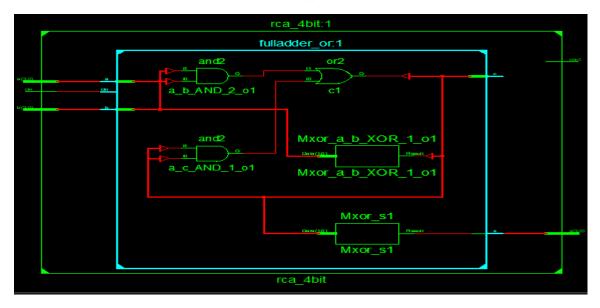

**3.2.1 Ripple Carry Adder (RCA) :** Multi-bit addition is performed by the RCA and moreover the processing delay is also increased by it. RCA is formed by cascading full adders in series. Each FA generates a carry which is provided to next FA and the process goes on, which is shown in Figure 3.3. The delay is increased, when the numbers of bits go on increasing. The advantage of RCA is its easy implementation and simple design.

Figure 3.3: 4 bit Ripple Carry Adder

Figure 3.4: RTL Schematic of Ripple Carry Adder

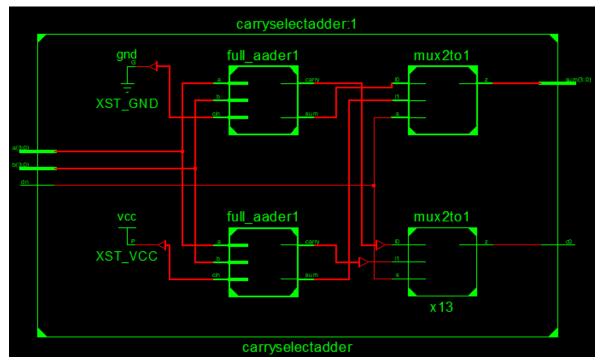

**3.2.2 Carry Select Adder (CSLA) :** CSLA is formed by two RCA and 2:1 multiplexer. Independent generation of sum and carry i.e.  $c_{in}=1$  and  $c_{in}=0$  are executed parallelly in CSLA. Correct sum along with correct carry-out is then selected by the multiplexer, depending on real carry-out of previous section. CSLA is further divided into two blocks i.e. uniform and variable block. More hardware is used by CSLA even though it gives less delay compared the ripple carry adder. 4- bit CSLA is shown in Figure 3.5 and RTL Schematic in Figure 3.6..

Figure 3.5: 4-bit Carry Select Adder

Figure 3.6: RTL Schematic of Carry Select Adder

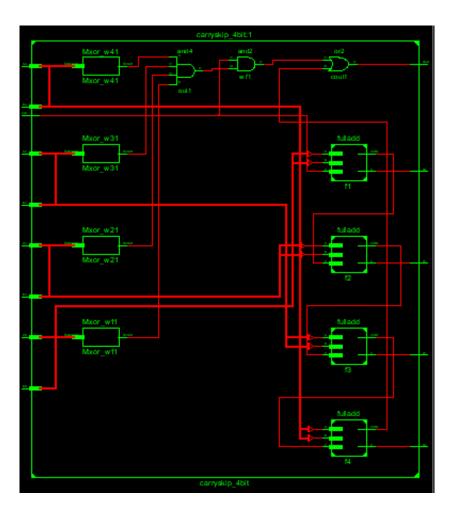

**3.2.3** Carry Skip Adder (CSkA) : This adder enhances delay of RCA with small effort. As the name indicates, CSkA uses skip logic in the propagation of carry. It is designed to speed up a wide adder by adding the propagation of carry bit around a portion of the entire adder. The carryin bit designated as  $C_i$ . The output of RCA (the last stage) is  $C_{i+4}$ . The carry skip circuitry consists of two logic AND gate which accepts the carry-in bit and compares it with the group of propagated signals using the individual propagate values.

$$P_{[i,i+3]} = (P_{i+3}) \cdot (P_{i+2}) \cdot (P_{i+1}) \cdot P_i$$

(3.5)

Output stage is produced when the output from the AND gate is ORed with  $C_{out}$  of RCA. Final carry is expressed by output stage which is represented by Equation 3.6.

Carry =

$$C_{i+4} + (P_{i,i+3}) \cdot C_i$$

(3.6)

If  $P_{[i,i+3]} = 0$ , then the Carry-out of the group is determined by the value of  $C_{i+4}$ . However, if  $P_{[i,i+3]} = 1$  then the Carry-in bit is  $C_i = 1$ , then the group carry-in is automatically sent to the next group of adders. The design of schematic of CSkA is shown in Figure 3.7.

Figure 3.7: 4-bit Carry Skip Adder

Figure 3.8: RTL Schematic of Carry Skip Adder

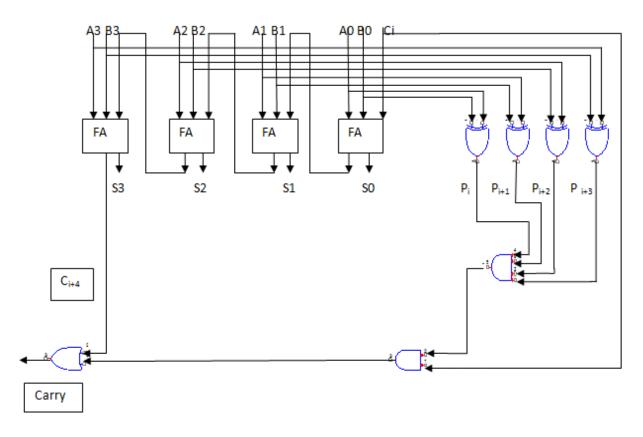

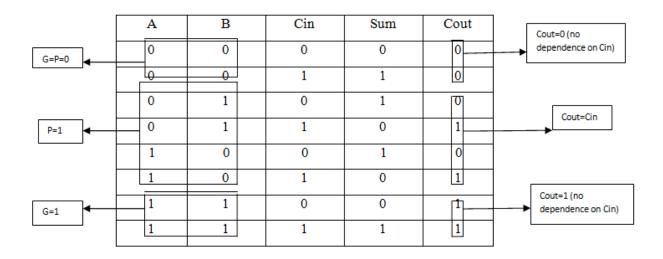

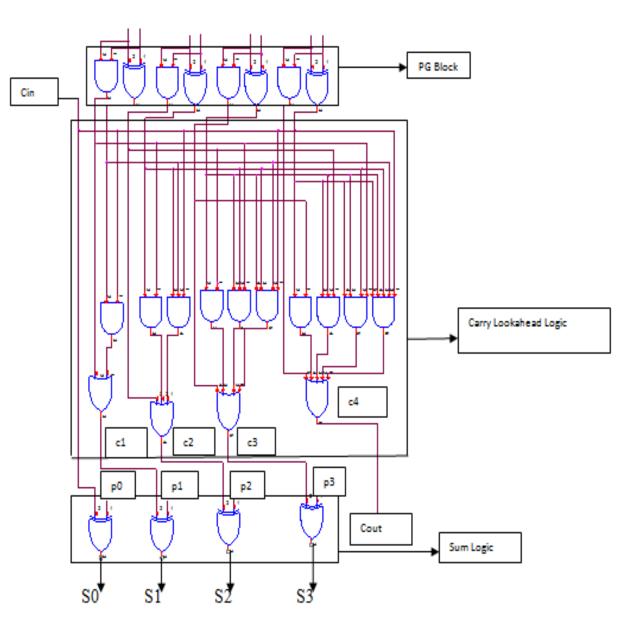

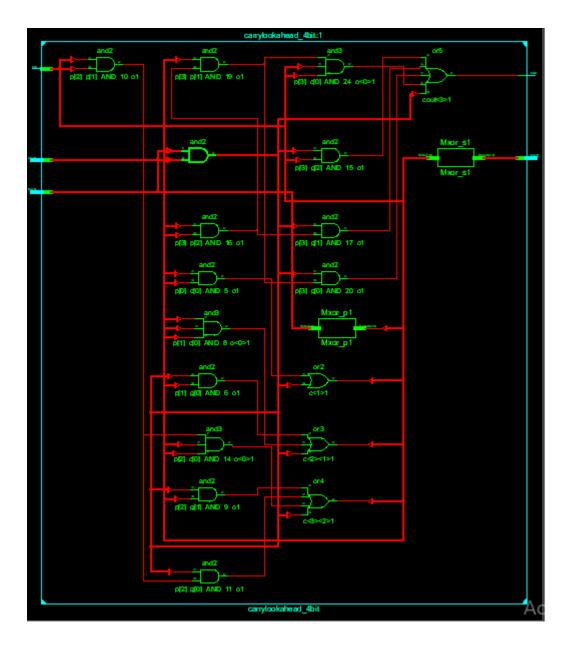

**3.2.4 Carry Look Ahead Adder (CLA)** The RCA is simple and easy to implement, but it suffers from serious delay issues. This is because the next stage of full adder needs to wait for Carry bit from the previous stage full adder The CLA solves this problem by calculating the carry signals in advance, based on the input signals. CLA technique is to drive the 'Sum' and 'Carry' outputs by using intermediate terms defined as 'Generate (G)' and 'Propagate (P)' terms. In the case of propagate the 'Carry-out' depends on the 'Carry-in' and in the case of generate the 'Carry-out' independent of the 'Carry-in'.

The Table 3.2 illustrates the concept of Propagate and Generate more clearly. The output 'Sum' and 'Carry' of the full adder in terms of P and G, can be observed from Table 3.2 as expressed by Equation 3.7 and Equation 3.8:

$$S_i = P_i \bigoplus C_i \tag{3.7}$$

$$C_{i+1} = G_i + (P_i . C_i)$$

(3.8)

#### Table 3.2: Truth Table of a Full Adder

Weinberger and Smith proposed a method for fast carry generation which states that the carry need not depend on the previous carry which is shown in Figure 3.9. Generate term produces a carry-out independent of the carry-in, i.e.no matter what the carry-in, the carry-out is always '1', when both of the inputs A and B are '1' thus G=A.B. The Propagate term transfers the input Carry as output Carry when only one of the inputs is high. The carry generation is done by first calculating Generate( $g_i$ ) and Propagate ( $p_i$ ) which is explained by Equation 3.9 and Equation 3.10 respectively.

$$g_i = A_i \cdot B_i \tag{3.9}$$

$$p_i = A_i \bigoplus B_i \tag{3.10}$$

Carry is generated by Equation 3.11 as:

$$C_i = g_{i-1} + p_{i-1} C_{i-1} \tag{3.11}$$

After the generation of carry, the sum is calculated using the Equation 3.12.

$$S_i = A_i \bigoplus B_i \bigoplus C_i \tag{3.12}$$

For wide adders where N > 16 (N is the input operand size), the delay of the carry look-ahead adders becomes dominated by the delay of passing the carry through the look-ahead stages and the implementation need high fan-in gates.

A0 B0 A1 B1 A2 B2 A3 B3

Figure 3.9: 4-bit Weinberger-Smith CLA

Figure 3.10: RTL Schematic of Carry Lookahead adder

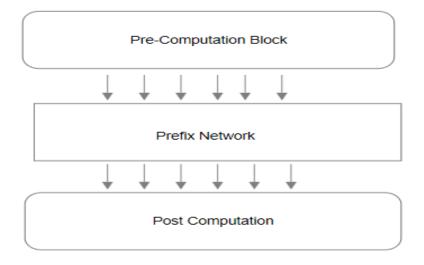

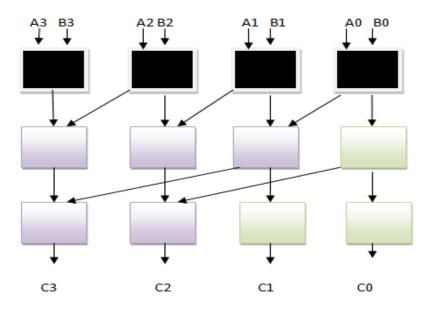

**3.2.5 Kogge Stone Adder (KSA) :** It is basically a prefix based adder. Prefix adder includes three stages i.e: pre-computation stage, prefix network stage and post-computation stage which is shown in Figure 3.11.

**1.** *Pre-Computation* -It computes the carry 'Propagate' and carry 'Generate' bits for each input pair as given by Equation 3.13 and Equation 3.14.

(3.13)

Propagate,  $P_i = A_i \text{ XOR } B_i$

(3.14)

Figure 3.11: Block level diagram of a prefix adder

Figure 3.12: 4-bit Kogge-Stone prefix adder

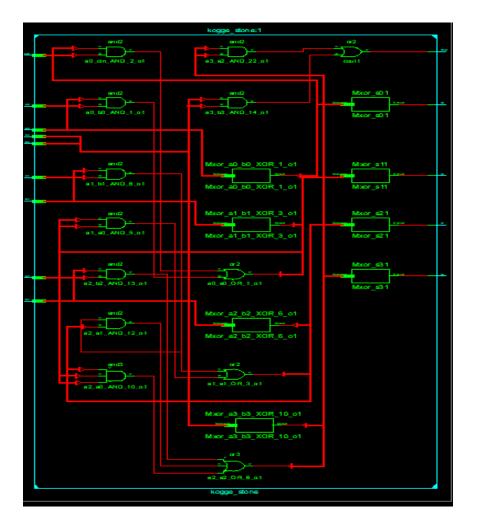

Figure 3.13: RTL Schematic of Kogge stone adder

**2.** *Prefix Network* - It computes the final carry from the carry 'Propagate' and carry 'Generate' bits which is expressed by Equation 3.15 and Equation 3.16.

Propagate,

$$P = P_i$$

AND  $P_{iprev}$  (3.15)

Generate,

$$G = (P_i \text{ AND } G_{iprev}) \text{ OR } G_i$$

(3.16)

**3.** *Post Computation* - It computes the final Sum from carry generated in the prefix network stage. Final sum and final carry is expressed by Equation 3.17 and Equation 3.18 respectively.

$$Sum, S_i = P_i XOR C_{i-1}$$

(3.17)

$$Carry, C_i = G_i \tag{3.18}$$

The KSA is the parallel prefix form that takes more area to implement, but has a lower fan-out at each stage. KSA started being used in multi-bit addition for faster addition but wiring congestion is often a problem. The KSA tree structure of 4 bit has been shown in Figure 3.8.

Figure 3.14 shows the colored representation of Figure 3.12. This figure also explains the equations for calculating Propagate and generates terms.

Figure 3.14: Representation of each KSA block

# **3.3** Implementation of 4-bit Adders

For implementation of 4-bit adders we have used Xilinx ISE 14.1 Design Suite, area and delay values are calculated from synthesis report while Power is calculated by Power analyzer in which we have calculated IOs Power and Leakage Power. The terms used in Table 3.3 are explained as follows:

- a) Look-Up Tables (LUT):- In Configurable Logic Block (CLBs) function generators are implemented using LUT. When LUT's inputs are given then a block of SRAM is indexed. The output of LUT depends on whatever value is in indexed location in its SRAM. This is because when chip is powered up, contents have to initialize and as RAM is volatile.

- b) **Slices:** In FPGA slices are the basic building block components. Before mapping the logic of design, number of elements which each slice contain make up. All of the Flip

flop and LUT's are packed into slices after mapping, not necessarily filling the slices. In the map report, even partially used slice is counted in the "occupied slices".

- c) **Input/output Block** (**IOB**):- In FPGA device, input and output functions are implemented from the grouping of basic elements. Such collection and grouping of basic elements is termed as an IOB.

- d) Delay: Delay is the time required for the input to be propagated to the output. In other words, the delay of a logic gate is defined as the time it takes for the effect of a change in input to be visible at the output

- **Router delay:** Router delay can be ~40% of total delay.

- Logic delay: Logic delay can be more than 50% of total delay.

- e) **Power: -** Power dissipation of two types a) static b) dynamic.

- Static power dissipation- Static power lost is due to current leakage in the transistors of an FPGA.

- Dynamic power dissipation- Dynamic power consumption is caused by signal alteration.

Table 3.3 shows the comparison of different adders for various performance parameters.

| Sr. |                              | No.<br>of 4<br>I/P<br>LUT | No.<br>of<br>occup<br>ied<br>slices | No. of<br>bonded IOB |          | Delay (ns)     |                 | Power<br>Total (W) |                  | Power Delay |

|-----|------------------------------|---------------------------|-------------------------------------|----------------------|----------|----------------|-----------------|--------------------|------------------|-------------|

| No. | Design                       |                           |                                     | I-<br>Buf            | O<br>Buf | Logic<br>Delay | Router<br>Delay | Power<br>IOs       | Power<br>Leakage | Product     |

| 1.  | 4 bit RCA                    | 8                         | 4                                   | 9                    | 5        | 7.306          | 2.768           | 0.021              | 0.034            | 0.543       |

| 2.  | 4 bit<br>Carry<br>Skip adder | 10                        | 6                                   | 9                    | 5        | 6.602          | 2.134           | 0.012              | 0.034            | 0.401       |

| 3.  | 4 bit<br>Carry<br>Select     | 11                        | 6                                   | 9                    | 5        | 6.637          | 2.099           | 0.021              | 0.034            | 0.471       |

Table 3.3: Area, Delay and Calculation of different 4-bit adders

|    | adder                                 |   |   |   |   |       |       |       |       |       |

|----|---------------------------------------|---|---|---|---|-------|-------|-------|-------|-------|

| 4. | 4 bit<br>Carry look<br>ahead<br>adder | 8 | 4 | 9 | 5 | 7.306 | 2.576 | 0.008 | 0.034 | 0.415 |

| 5. | 4 bit<br>Kogge<br>stone<br>adder      | 7 | 4 | 9 | 5 | 6.602 | 2.006 | 0.008 | 0.034 | 0.361 |

## 3.4 Proposed Adder

Among the parallel adders *Carry Increment Adder (CIA)* has the best delay performance which is one of the most important parameter in the high speed devices. The resulting CIA cuts the circuit size down by 23% with no change in performance. CIA is preferred for large word lengths (upto 128 bits) as the power delay product is smallest among all the known adder architectures. An 8bit CIA adder includes two blocks of adder each 4 bit. In CIA only one partial sum is calculated and incremented if necessary, according to the input carry but in Carry select adder, from each group computing two partial sums and selecting the correct one. We have implemented modified 8-bit CIA using KSA which provides less delay then already implemented 8-bit CIA. As we have seen from Table 3.3, among all the 4-bit adders KSA has the best performance in terms of delay i.e. 8.608ns. Therefore, we have used KSA to implement 8-bit CIA.

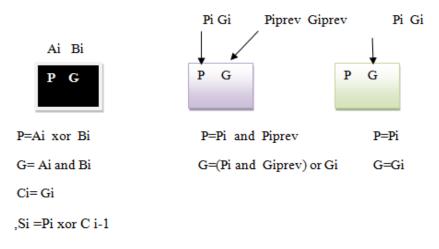

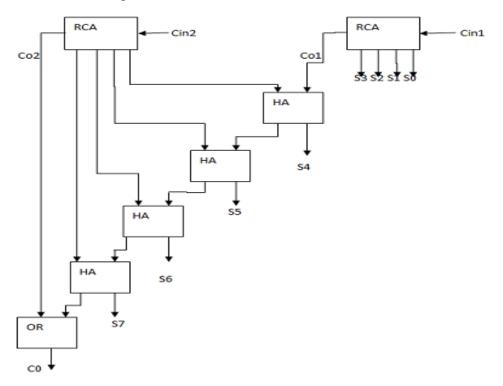

a) CIA using RCA: CIA consists of incremental circuitry and RCA's. A desired number of 4bit inputs add by RCA and generating partitioned sum and partitioned carry. Using HA's in ripple carry sequence with an in order the incremental circuit is calculated. For example, two 4-bit RCA is required to implement an 8-bit CIA. From the first block of RCA, we directly get the 4-bit sum of CIA. And the first RCA block carry output is given as input to the C<sub>in</sub> of an incremental circuit. The incremental circuit consists of half adders and the second RCA block the partial sum obtained is given to incremental circuit. The block diagram of an 8-bit CIA\_RCA is shown in Figure 3.15.

Figure 3.15: Block diagram of CIA\_RCA

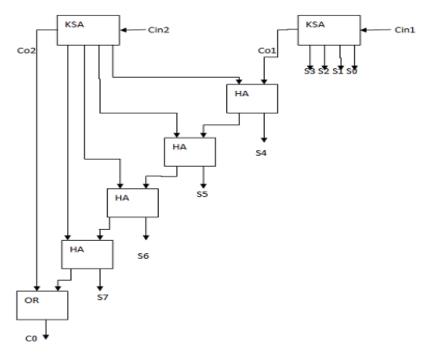

b) CIA using KSA: The KSA replaces the ripple carry adder, in order to reduce the delay of the regular CIA. The modified 8-bit CIA using KSA is shown in Figure9. KSA suffer from complexity in prefix network due to an increase in number of wiring and logic cells. A delay efficient KSA is proposed. Among the parallel adders carry increment adder has the best performance which is one of the most important parameter in the high speed devices. The proposed design is a new concept and to the best of our knowledge it has not been proposed earlier by any researcher. In this sub section, we present the modified Carry increment adder i.e. CIA\_KSA. We know that RCA design is simple and implementation is easy, but it suffers from worst propagation delay. It is proved that KSA performs better than RCA in term delay at the expense of increased design complexity. We have modified CIA\_RCA by replacing the RCA block with KSA block. Because of the property of KSA, the overall delay performance will be improved. As similar to CIA\_RCA incremental circuit can be calculated

using HA's in ripple carry sequence with an in order. The block diagram representation of CIA\_KSA is shown in Figure 3.16 and RTL schematic in Figure 3.18.

### Figure 3.16: Block diagram of CIA\_KSA

From the synthesis report, the performance parameters like area and delay are obtained and from power analyzer power is calculated which is shown in Table 3.4. It can be observed that the proposed design for 8bit Carry increment adder has better delay performance which is the desired goal of this research work.

| Sr. | Design                      | No.<br>of 4<br>I/P | No.<br>of<br>occup |            | . Of<br>ed IOB | Dela           | y (ns)          |              | ower<br>al (W)   | Power<br>Delay<br>Product |

|-----|-----------------------------|--------------------|--------------------|------------|----------------|----------------|-----------------|--------------|------------------|---------------------------|

| No. |                             | LUT                | ied<br>slices      | I –<br>Buf | O-<br>Buf      | Logic<br>Delay | Router<br>Delay | Power<br>IOs | Power<br>Leakage | Frouuct                   |

| 1.  | 8bit<br>CIA_RCA             | 19                 | 11                 | 18         | 9              | 9.418          | 4.502           | 0.008        | 0.034            | 0.585                     |

| 2.  | 8bit<br>Proposed<br>CIA_KSA | 21                 | 12                 | 18         | 9              | 8.714          | 3.631           | 0.021        | 0.034            | 0.666                     |

Table 3.4: Area, Delay and Power calculation of 8 bit CIA

Figure 3.17: RTL Schematic of CIA\_RCA

Figure 3.18: RTL Schematic of CIA\_KSA

# **3.5 Comparison Table**

Table 3.5 signifies the comparison of designed 8-bit CIA with the existing adder. Our proposed circuit gives the best delay i.e. 12.345 ns for CIA\_KSA in comparison with Devi A.B. *et al.* 2016 [11] whose delay is 14.59 ns for CIA\_RCA and 13.54 ns for CIA\_CLA.

|                                            | No. Of occupied<br>Slices | LUTs | Delay(ns) | Power(W) |

|--------------------------------------------|---------------------------|------|-----------|----------|

| Proposed Work<br>CIA_KSA                   | 12                        | 21   | 12.345    | 0.054    |

| Devi AB <i>et al.</i> 2016 [20]<br>CIA_RCA | 13                        | 20   | 14.59     | 0.041    |

| Devi AB <i>et al.</i> 2016 [11]<br>CIA_CLA | 12                        | 19   | 13.54     | 0.041    |

Table 3.5: Delay and Power calculation of 8-bit CIA using KSA

# **3.6 Conclusion**

The performance of any circuit in VLSI design limits by the constituent factors like power, delay and area. In this chapter a modified carry increment adder is proposed using KSA instead of ripple carry adder. Without affecting the circuit the delay performance of the circuit is improved by replacing the 4-bit RCA with a proposed 4-bit KSA. But the proposed CIA\_KSA has the disadvantage of more power consumption. The design is tested and verified by Verilog HDL coding and simulation is carried out by in Xilinx ISE 14.1 design suite and synthesized for Spartan 3E FPGA. The delay performance of KSA is better than RCA but as operand size increases (32-bits and above). KSA suffers from complexity due to an increase in the number of logic cells and wiring. Future work may be dedicated to studying the complexity of CIA\_KSA when the number of bits was increased.

# CHAPTER 4 MULTIPLIERS

Multiplication is the mathematical operation that at its simplest is an abbreviated process of adding an integer to itself, a specified number of times and can be measured as a chain of repeated additions. The number which is to be added is called the multiplicand, the number of times which is added is called the multiplier and the result being given is known as the product. Multiplication is an important fundamental function in arithmetic operations. Many researchers have tied and are trying to design multiplier which offers either of the following- high speed, less area and low power consumption. We describe different types of multipliers: Array multiplier, Wallace tree multiplier, Vedic multiplier. Designer mainly concentrates on efficient circuit design. Characteristics of an efficient multiplier: *Speed*-At high speed multiplier should perform operation, *Accuracy*- Correct result should given by good multiplier, *Area*- Less number of LUTs and Slices are occupied by multiplier and *Power*- The power consumed by the multiplier is less.

Three main steps of multiplication process:-

- 1. Generation of partial product

- 2. Addition of partial product

- 3. Final addition

Figure 4.1: Block diagram of Multiplier architecture

Block diagram consist of three stages, in the first stage partial products are generated by multiplying bit by bit of multiplier and multiplicand. In the next stage there is addition of generated partial product, this stage is complex and the speed of circuit is derived and last stage

generated the output result by added the two-row outputs. Parallel multipliers are the most rapid multiplier type. The earlier performance of multiplier is enhanced to developed number of technique.

Let the multiplicand and multiplier be A and B:

$$A = a_{(M-1)} \cdot a_{(M-2)} \dots \cdot a_1 a_0 = \sum_{i=0}^{M-1} a_i \cdot 2^i$$

(4.1)

$$\mathbf{B} = \mathbf{b}_{(N-1)} \cdot \mathbf{b}_{(N-2)} \dots \cdot \mathbf{b}_1 \mathbf{b}_0 = \sum_{i=0}^{N-1} \mathbf{b}_i \cdot 2^i \tag{4.2}$$

The value of their product  $P = A \times B$  is given by Equation 4.3:

$$P = \sum_{i=0}^{M-1} \sum_{i=0}^{N-1} (a_i b_i . 2^{i+j})$$

(4.3)

Equation 4.4 and 4.5 expressed signed binary number and Equation 4.6 defined the product of A and B.

$$A = -a_{M-1} \cdot 2^{M-1} + \sum_{i=0}^{M-2} a_i \cdot 2^i$$

(4.4)

$$B = -b_{N-1} \cdot 2^{N-1} + \sum_{i=0}^{N-2} b_i \cdot 2^i$$

(4.5)

The product  $P=A \times B$  is given by Equation 4.6:

$$\mathbf{P} = (-a_{M-1} \cdot 2^{M-1} + \sum_{i=0}^{M-2} a_i \cdot 2^i) \times (-b_{N-1} \cdot 2^{N-1} + \sum_{i=0}^{N-2} b_i \cdot 2^i)$$

(4.6)

## 4.1 Different Multipliers

#### 4.1.1 Array Multiplier

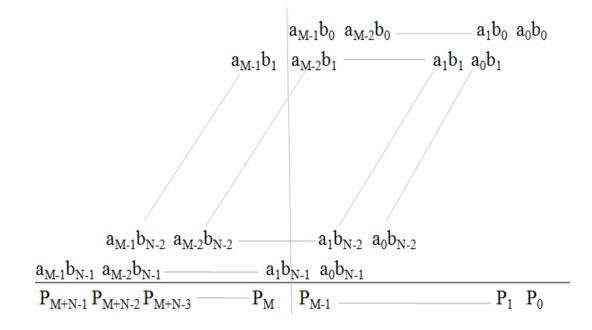

It is regular in structure and to go from one block to adjacent block short wires are used. In VLSI its layout is efficient and simple. N partial product is generated when there is multiplication of multiplier and multiplicand bit by bit as expressed by Equation 4.3. Multiplication is depends on Add/Shift algorithm. Figure 4.2 shows the  $M \times N$  multiply operation of array multiplier and by ANDing multiplicand and multiplier partial products are generated.  $4 \times 4$  array multiplier is shown in Fig.4.3.

Figure 4.2: Partial product array for an M×N multiplier

Figure 4.3: 4×4 Array multiplier

Figure 4.4: RTL Schematic of 4 bit Array multiplier

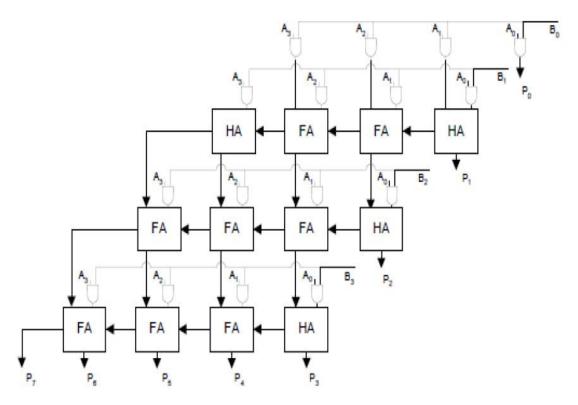

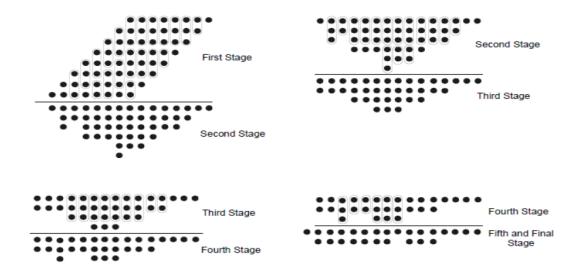

# 4.1.2 Wallace multiplier

In this multiplier there is parallel addition of generated partial products, so it takes less time for accumulation than array multiplier because in array multiplier the partial products are added in series.  $8\times8$  bit partial product reduction is shown in Figure 4.5. In this Figure the two circled dots represent HA and tree circled dots represent FA. After four stages partial product is reduced to two rows. To reduce tree structure there are so many ways but only one method of reduction is shown.

Figure 4.5: 8×8 partial product tree reduction of Wallace multiplier

Figure 4.6: RTL Schematic of 4 bit Wallace multiplier

## 4.1.3 Vedic Multiplier

The word "Vedic" is derived from the word "Veda" which means the store house of knowledge. Veda consist of 16 sutras which encapsulate the branches of Mathematics- geometry, calculus, arithmetic, trigonometry etc. These sutras are : Shunyamanyat(Anurupye), Chalana-Kalanabyham, Ekadhikina Purvena, Purvena, Ekanyunena Gunakasamuchyah, Gunitasamuchyah, Nikhilam Navatashcaramam Dashatah, Paraavartya Yojayet, Shesanyankena Charamena, Shunyam Puranapuranaabhyam, Sankalana-vyavakalanabhyam, Sopaantyadvayamantyam, Saamyasamuccaye, Urdhva-tiryakbyham, Vyashtisamanstih, Yaavadunam.

## Vedic Multiplier using "UrdhvaTiryakbyham" Sutra:

In Sanskrit literature the 'Urdhva' means 'vertically' and 'Tiryakbyham' means 'crosswise'. UrdhvaTiryakbyham is applicable to all cases of multiplication. In one step the algorithm produces sum and partial product. Once the number of bits is increased, this multiplier is advantageous as compared to other multipliers in terms of area and gate delay increases slowly.

| For example: | 131 | × | 121 |

|--------------|-----|---|-----|

|--------------|-----|---|-----|

| Step | Explanation           | Process      | Result   |

|------|-----------------------|--------------|----------|

|      | The numbers that      |              |          |

|      | lie on ones place are |              |          |

|      | multiplied vertically | 1 3 1        | Result=1 |

| 1.   | and output is         | Ļ            | Carry=0  |

| 1.   | generated and         | <u>1 2 1</u> | Curry=0  |

|      | stored result in ones | 1            |          |

|      | place of the final    |              |          |

|      | result                |              |          |

|    | The numbers that          |                                       |                |

|----|---------------------------|---------------------------------------|----------------|

|    | lie on ones and tens      |                                       |                |

|    | place are multiplied      | $1 \ 3 \ 1$                           | Result=3+2=5   |

| 2. | by crossover              | X                                     | Carry=0        |

| ۷. | multiplication and        | <u> </u>                              | Carry=0        |

|    | result is stored on       | 5 1                                   |                |

|    | tens place                |                                       |                |

|    | The numbers that          |                                       |                |

|    | lie on ones and           |                                       |                |

|    | hundred place are         |                                       |                |

|    | multiplied by             |                                       |                |

|    | crossover                 |                                       |                |

|    | multiplication and        |                                       |                |

|    | number that lie on        | 1 3 1                                 |                |

|    |                           |                                       | Result=1+6+1=8 |

| 3. | hundred place are         |                                       | Carry=0        |

|    | multiplied by<br>vertical | $\frac{1}{8} \frac{2}{5} \frac{1}{1}$ |                |

|    |                           | 8 3 1                                 |                |

|    | multiplication,           |                                       |                |

|    | result of these           |                                       |                |

|    | multiplication are        |                                       |                |

|    | summed and final          |                                       |                |

|    | result stored in          |                                       |                |

|    | hundred place.            |                                       |                |

|    | The numbers that          |                                       |                |

|    | lie on tens and           | 1 2 1                                 |                |

|    | hundred place are         | $\downarrow 1 3 1$                    | Result=3+2=5   |

| 4. | multiplied by             | A                                     | Carry=0        |

|    | crossover                 | $\frac{1 \ 2 \ 1}{2 \ 2 \ 2}$         |                |

|    | multiplication and        | 5851                                  |                |

|    | result is stored on       |                                       |                |

|    | thousand place            |                                       |                |

| 5. | Finally, Vertical<br>multiplication of<br>two numbers on<br>hundred place are<br>multiplied, 1 bit<br>output is generated<br>and stored result in<br>ten thousand place<br>of the final result | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | Result=1<br>Carry=0 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|

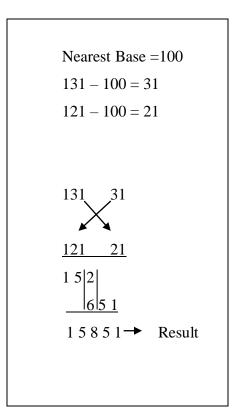

## Nikhilam Sutra

It literally means "all from 9 and last from 10" and when large numbers are involved it is more efficient. When the original number is larger the multiplication complexity is lesser. To perform the multiplication the compliment of the large number is find out from its nearest base.

For example:  $131 \times 121$

Figure 4.7: RTL Schematic of 4 bit Vedic multiplier

# 4.2 Implementation of 4- bit multipliers

For implementation of 4-bit multipliers we have used Xilinx ISE 14.1 Design Suite, area and delay values are calculated from synthesis report while Power is calculated by Power analyzer in

which we calculated IOs Power and Leakage Power. The comparison of different multipliers in terms of area, delay and power is shown in Table 4.1

| Sr.<br>No. Design | Decise                             | No.<br>of 4<br>I/P<br>LUT | No.<br>of<br>occup<br>ied<br>slices | No. of<br>bonded<br>IOB |            | Delay (ns)     |                 | Power<br>Total (W) |                  | Power Delay<br>Product |

|-------------------|------------------------------------|---------------------------|-------------------------------------|-------------------------|------------|----------------|-----------------|--------------------|------------------|------------------------|

|                   | Design                             |                           |                                     | I-<br>Buf               | O –<br>Buf | Logic<br>Delay | Router<br>Delay | Power<br>IOs       | Power<br>Leakage |                        |

| 1.                | 4 bit<br>Array<br>multipli<br>er   | 29                        | 17                                  | 8                       | 8          | 9.171          | 4.486           | 0.001              | 0.034            | 0.4779                 |

| 2.                | 4 bit<br>Wallace<br>multipli<br>er | 33                        | 19                                  | 8                       | 9          | 7.947          | 3.928           | 0.001              | 0.034            | 0.4156                 |

| 3.                | 4 bit<br>Vedic<br>multipli<br>er   | 39                        | 22                                  | 9                       | 9          | 8.837          | 3.995           | 0.029              | 0.034            | 0.8084                 |

Table 4.1: Area, Delay and Power calculation of 4-bit Multipliers

## 4.3 **Proposed Design**

8-bit multipliers are implemented using Kogge stone adder(KSA). Among all the adders KSA is best in term of performance i.e. delay, speed and it is basically a prefix based adder. We have implemented Array multiplier, Vedic multiplier, Wallace multiplier using KSA for different performance parameters. In term of delay Wallace multipliers have best delay i.e. 18.024ns but there are increased in power consumption. On the other hand in Array multiplier and Vedic multiplier there is decrease in the speed and decrease in the power consumption. Each multiplier has its own advantage and disadvantage depending on logic we are using.

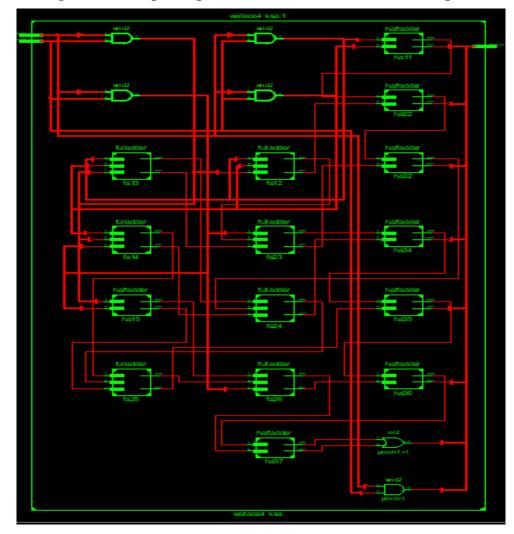

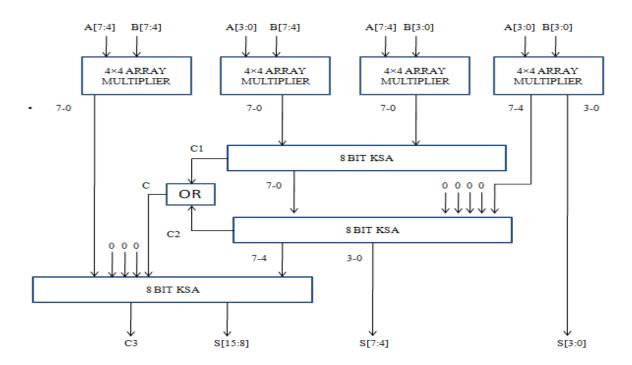

#### 8×8 Array Multiplier

8 by 8 Array multiplier is implemented by considering two 8-bits binary numbers A[7:0] and B[7:0]. To implement 8 X 8 Array multiplier, 4 X 4 Array multipliers are used to generate partial products. For addition of generated partial product, three KSA of 8 bit are used. We are taking four 4 X 4 Array multiplier block, in the first block least significant bits(LSBs) of A and B are multiplied to generate S[3:0] of final result. In second block most significant bits(MSBs) of A is multiplied with LSBs of B to generate input bits for first block of KSA and in third block LSBs of A is multiplied with MSBs of B to generate input bits for first block of KSA. In fourth block, MSBs of A and B are multiplied to generated from these adders are ORed. By ORing these two KSA a carry is generated which is applied a input to next KSA. In some blocks of KSA zero inputs are applied according to the requirement. KSA arrangement are made in such way that the speed of working is increased. Finally sum[15:0] and carry(C3) is generated and architecture of 8 X 8 Array multiplier is shown in Figure 4.8.

Figure 4.8: 8×8 Array multiplier architecture

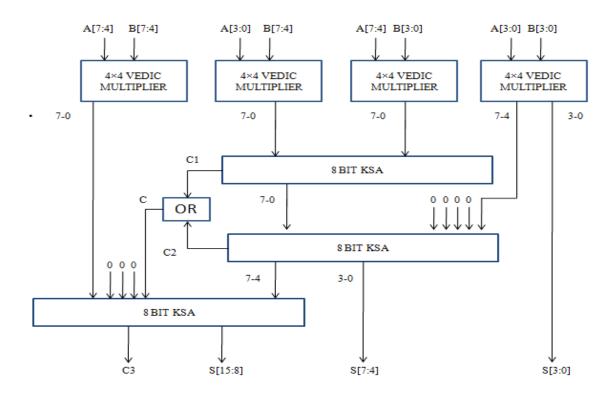

#### 8 X 8 Vedic Multiplier

8 by 8 Vedic multiplier is implemented by considering two 8-bits binary numbers A[7:0] and B[7:0]. To implement 8 X 8 Vedic multiplier, 4 X 4 Vedic multipliers are used to generate partial products. For addition of generated partial product, three KSA of 8 bit are used. We are taking four 4 X 4 Vedic multiplier block, in the first block least significant bits(LSBs) of A and B are multiplied to generate S[3:0] of final result. In second block most significant bits(MSBs) of A is multiplied with LSBs of B to generate input bits for first block of KSA and in third block LSBs of A is multiplied with MSBs of B to generate input bits for first block of KSA. In fourth block, MSBs of A and B are multiplied to generated from these adders are ORed. By ORing these two KSA a carry is generated which is applied a input to next KSA. In some blocks of KSA zero inputs are applied according to the requirement. KSA arrangement are made in such way that the speed of working is increased. Finally sum[15:0] and carry(C3) is generated and architecture of 8 X 8 Vedic multiplier is shown in Figure 4.9.

Figure 4.9: 8×8 Vedic multiplier architecture

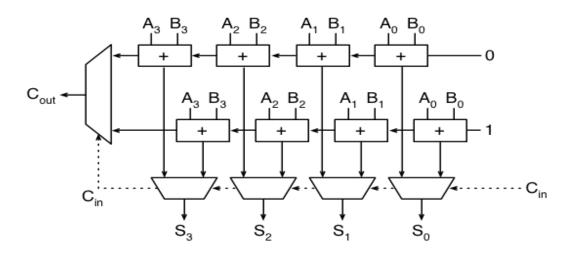

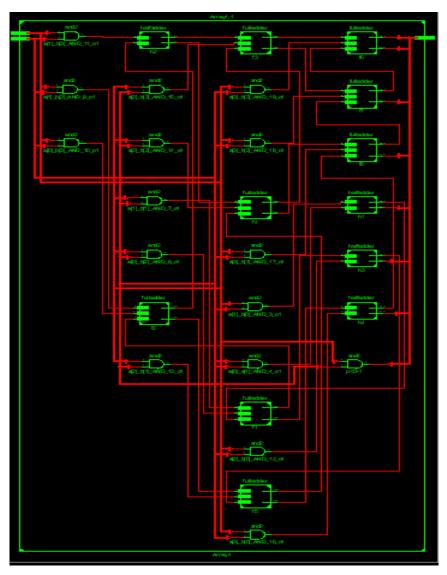

#### 8 X 8 Wallace Multiplier

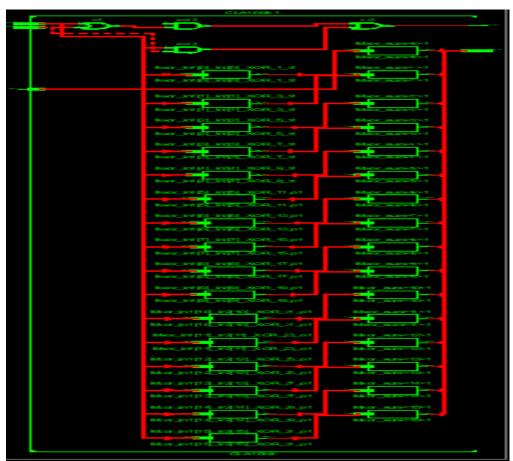

8 by 8 Wallace multiplier is implemented by considering two 8-bits binary numbers A[7:0] and B[7:0]. To implement 8 X 8 Wallace multiplier, 4 X 4 Wallace multipliers are used to generate partial products. For addition of generated partial product, three KSA of 8 bit are used. We are taking four 4 X 4 Wallace multiplier block, in the first block least significant bits (LSBs) of A and B are multiplied to generate S[3:0] of final result. In second block most significant bits(MSBs) of A is multiplied with LSBs of B to generate input bits for first block of KSA and in third block LSBs of A is multiplied with MSBs of B to generate input bits for first block of KSA. In fourth block, MSBs of A and B are multiplied to generated from these adders are ORed. By ORing these two KSA a carry is generated which is applied a input to next KSA. In some blocks of KSA zero inputs are applied according to the requirement. KSA arrangement is made in such way that the speed of working is increased. Finally sum[15:0] and carry(C3) is generated and architecture of 8 X 8 Wallace multiplier is shown in Figure 4.7 and RTL schematic in Figure 4.10.

Figure 4.10: 8×8 Wallace multiplier architectur

| Sr.<br>Design |                 | No.<br>of 4<br>I/P | No. of<br>occupi<br>ed | No.<br>bonde | Of<br>d IOB | Dela   | y (ns) | _     | ower<br>al (W) | Power<br>Delay<br>Product |

|---------------|-----------------|--------------------|------------------------|--------------|-------------|--------|--------|-------|----------------|---------------------------|

| 1100          |                 | LUT                | slices                 | I –          | 0-          | Logic  | Router | Power | Power          | Troduct                   |

|               |                 | LUI                | snces                  | Buf          | Buf         | Delay  | Delay  | IOs   | Leakage        |                           |

| 1.            | Wallace_<br>KSA | 183                | 104                    | 19           | 17          | 11.285 | 6.739  | 0.012 | 0.034          | 0.8291                    |

| 2.            | Array_K<br>SA   | 171                | 98                     | 19           | 17          | 13.121 | 7.850  | 0.001 | 0.034          | 0.7339                    |

| 3.            | Vedic_K<br>SA   | 216                | 120                    | 17           | 17          | 14.011 | 8.104  | 0.001 | 0.034          | 0.7740                    |

Table 4.2: Area, Delay and Power calculation of 8 bit Multipliers

Table 4.3 gives the comparison of designed 8-bit Wallace multiplier with the existing multiplier. Our proposed circuit of which multipliers gives the less delay i.e. 18.024 ns in comparison Rajaram S *et al.* 2011[6] whose calculated delay is 27.457 ns and Thomas A *et al.* 2016[33] whose delay is 39 ns. We have also calculated power which is less i.e. 46mW then Murugeswari S. *et al.* 2014[4] whose power is 264mW, 231mW while Rajaram S *et al.* 2011[6] has not reported any power.

|                                                                   | Width | No. of occupied slices | No. of LUTs | Delay(ns) | Power(mW) |

|-------------------------------------------------------------------|-------|------------------------|-------------|-----------|-----------|

| Propsed work<br>Using KSA                                         | 8     | 104                    | 183         | 18.024    | 46        |

| Rajaram         S         et         al.           2011[6]        | 8     | -                      | -           | 27.457    | -         |

| Murugeswari S. <i>et al.</i> 2014[4]<br>Using Full adder          | 8     | 87                     | 163         | 17.223    | 264       |

| Murugeswari S. et<br>al. 2014[4]<br>Using MUX based<br>Full adder | 8     | 84                     | 155         | 17.789    | 231       |

| Thomas A <i>et al.</i><br>2016[33]                                | 8     | -                      | 133         | 39        | -         |

Table 4.3: Area, Delay and Power calculation of 8 bit Wallace Multiplier

Table 4.4 gives the comparison of designed 8-bit VM with the existing multipliers. Our proposed circuit of which multiplier gives the best delay i.e 22.115ns in comparison Gokhale GR *et al.* 2015[3] whose delay is 44.358ns and Thomas A *et al.* 2016[33] whose delay is 34 ns using RCA and 30 ns using CLA. We have also calculated Power which is 35mW while Gokhale GR *et al.* 2015[3] and Anjana R *et al.* 2014[5] has not reported any power. Anjana R *et al.* 2014[5] calculated difference between logic delay and router delay which is 5.588ns and our proposed circuit difference between logic delay and router delay is 5.907 which is more but the no. of LUTs required is less than Anjana R *et al.* 2014[5].

|                                                 | Width | No. of LUTs | Area(gate<br>count) | Delay(ns) | Power(W) |

|-------------------------------------------------|-------|-------------|---------------------|-----------|----------|

| Propsed work<br>Using KSA                       | 8     | 216         | -                   | 22.115    | 0.035    |

| Gokhale GR <i>et al.</i><br>2015[3]             | 8     | -           | 1293                | 44.358    | -        |

| Anjana R <i>et al.</i><br>2014[5]               | 8     | 309         | -                   | 5.588     | -        |

| Thomas A et al.<br>2016[33]<br>Using RCA        | 8     | 166         | _                   | 34        | -        |

| Thomas A <i>et al.</i><br>2016[33]<br>Using CLA | 8     | 167         | -                   | 30        | -        |

Table 4.4: Area, Delay and Power calculation of 8 bit Vedic Multiplier

Table 4.5 gives the comparison of designed 8-bit AM with the existing multipliers. Our proposed circuit of which multiplier gives the best delay i.e. 20.971 ns in comparison to Maiti A *et al.* 2016[34] whose delay is 25.3 ns and Thomas A *et al.* 2016[33] whose delay is 44ns. We also calculated power which is more i.e 35 mW in comparison to Maiti A *et al.* 2016[34] whose power is 0.0606 mW.

Table 4.5: Area, Delay and Power calculation of 8 bit Array Multiplier

|                                              | Width | No. of LUTs | Delay(ns) | Power(mW) |

|----------------------------------------------|-------|-------------|-----------|-----------|

| Propsed work<br>Array Multiplier             | 8     | 171         | 20.971    | 35        |

| Maiti A <i>et al.</i> 2016[34]<br>Using CMOS | 8     | -           | 25.3      | 0.0606    |

| Thomas A <i>et al.</i><br>2016[33]           | 8     | 126         | 44        | -         |

It can be observed that the proposed design for 8bit Wallace Multiplier has better delay performance which was the desired goal of this research work.

### 4.4 Conclusion

The performance of any circuit in VLSI design limits by the constituent factors like power, delay and area. In this chapter Array multiplier, Vedic multiplier and Wallace multiplier are implemented using KSA. It is concluded that KSA have less delay and power as compared to other adders, so it is best suited for implementation of modified multiplier. Wallace multiplier has less delay compared to other multipliers but there is increase in power consumption. The design is tested and verified by Verilog HDL coding and simulation is carried out by in Xilinx ISE 14.1 design suite and synthesized for Spartan 3E FPGA. KSA suffers from complexity due to an increase in the number of logic cells and wiring. Future work may be dedicated to decrease in power consumption of Wallace multiplier.

# CHAPTER 5 FAST FOURIER TRANSFORMS

Fast Fourier Transform (FFT) is used for Signal Processing applications. It consists of addition and multiplication operations, whose speed improvement will enhance the accuracy and performance of FFT computation for any applications. FFT are used to covert signal from time domain to frequency domain. In FFT processing unit Butterfly Structure is the basic building block and is used for the calculating complex calculation. So, it is important to design an efficient adder and multiplier block and used that efficient block in Butterfly Structure.

# 5.1 Efficient Adder using 16 bit and 32 bit

Efficient adder for 4 bit and 8 bit has been already implemented in Chapter 2. We have analyzed that KSA and CLA are the best suited adders in terms of delay and power. Now we need to implement 16 bit and 32 bit KSA and CLA so, that they can be used in high performance applications.

## KSA

RCA has drawback that its delay goes on increasing as number of bits increases. To overcome this problem KSA is used. For high performance application large amount of bits are used for doing multiple calculation and tasks. So, there is a need to implement 32 bit KSA which is implemented by using 16 bit KSA. Firstly, it is important to implement 16 bit KSA. In KSA as the number of bits goes on increasing speed is increases but the drawback is that complexity increases. The KSA is the parallel prefix form that takes more area to implement. The RTL schematic of KSA for 16 bit and 32 bit are shown in Figure 5.1 and Figure 5.2.

Figure 5.1: RTL Schematic of 16 bit KSA

Figure 5.2: RTL Schematic of 32 bit KSA