# PERFORMANCE ASSESSMENT OF DEVICES BEYOND THE SCALING LIMITS— DOUBLE-GATE AND SURROUNDING-GATE MOSFET

### Dissertation submitted in partial fulfillment of the degree of

## Master of Technology

in

## Electronics and Communication Engineering

Under the Supervision of

### **Prof. GHANSHYAM SINGH**

by

### **HIMANGI SOOD**

#### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

JAYPEE UNIVERSITY OF INFORMATION TECHNOLOGY

SOLAN – 173 215, INDIA

Roll No. 132016

MAY-2015

### ABSTRACT

Complementary Metal Oxide Semiconductor (CMOS) technology advancement for improving the system reliability, current drive, computational capability and integration density at lower cost has reached to a limit where the significant undesirable effects appear, which further poses tremendous challenges beyond the 45 nm technology node. Therefore, for the further advancement of technology this would also be beneficial for the circuit designers as well as the communication market come with the more innovative device structures. Among which the double-gate MOSFET, due to increase in the mobility, ideal sub-threshold slope, high drain current, reduced power consumption and screening of source end of the channel by the drain electric field, and the surrounding-gate MOSFET, due to increase in gate control and, low-off state current, have emerged as better alternative device structures for the reduced short channel effects and achieving a compact device with a much reduced dimension. In this dissertation, an analytical modeling of both the devices is performed with the help of Poisson equation and gradual channel approximation. Moreover, the expressions are derived using the surface potential model based on drift-diffusion approximation, which is important for the future requirement of the technology. The modeling of terminal charges and trans-capacitances are also presented which are further used for the circuit simulation. Finally, for the small-signal analysis, the trans-capacitances are used to yield the Y-parameters and S-parameters of the device, which would characterize the device for the specified frequency regime of the spectrum for the application as an amplifier and as a switch in the wireless communication transceiver, based on the power gain analysis and on-state switch circuit analysis, respectively. In addition to this, the influence of the Gaussian doping in vertical direction (across the radius) of the surrounding-gate MOSFET on the device performance based on certain assumptions is also presented.

### ACKNOWLEDGMENT

With all the blessings of almighty we have finally completed this thesis.

Foremost, I would like to express my sincere gratefulness and indebtedness to my supervisor *Prof. Ghanshayam Singh* for the continuous support throughout my course. His motivation, patience and guidance helped me in all the time of research and writing of this thesis.

I am also thankful to *Prof. T.S Lamba*, Dean, Academic and Research and *Prof. Sunil V. Bhooshan*, Head, Department of Electronics and Communications for providing the research environment in the college.

Besides the supervisor, I would also like to thank the rest of my project jury members: *Dr. Davinder Singh Saini*, *Dr. Shruti Jain* and *Mr. Munish Sood* for their encouragement, insightful comments and suggestions, and hard questions. Moreover, wide knowledge of *Mr. Salman Raju Talluri* has also helped me whenever I was in a dilemma for the numerical analysis problems.

I thank my friends (*Aakanksha Sharma*, *Bindu Bharti*, *Versha Sharma*, *Subhash Tiwari*, and *Poonam Kango*) for motivating me whenever I was depressed, and for all the fun we have had in the last two years. My sincere thanks go to my lab mates *Keerti Tiwari*, *Shweta Pandit* and *Garima Bharti* for providing me an energetic environment in the lab.

Last but not the least, I would like to thank my family: my parents *Mr. Sumeet Sood* and *Mrs. Neelam Sood* and my elder sister, *Ms. Vaishali Sood*, for supporting me spiritually throughout my life.

Himangi Sood

## CONTENTS

| ABSTRACT                                      | i     |

|-----------------------------------------------|-------|

| ACKNOWLEDGMENT                                | ii    |

| LIST OF TABLES                                | v     |

| LIST OF FIGURES                               | vii   |

| LIST OF PUBLICATIONS                          | ix    |

|                                               |       |

| CHAPTER 1                                     | 1     |

| INTRODUCTION                                  | 2     |

| 1.1. MOSFET                                   | 3     |

| 1.2. Scaling                                  | 5     |

| 1.3. Short Channel Effects                    | 10    |

| 1.4. Advanced MOSFET Structures               | 18    |

| 1.4.1. Double Gate MOSFET                     | 20    |

| 1.4.2. Surrounding Gate MOSFET                | 27    |

| 1.5. Problem Statement                        | 30    |

| 1.6. Dissertation Organization                | 31    |

| CHAPTER 2                                     | 32    |

| PERFORMANCE ANALYSIS OF DOUBLE-GATE MOSFET    | 32    |

| 2.1. Introduction                             | 32    |

| 2.2. Symmetric Double Gate MOSFET             | 34    |

| 2.3. Analysis                                 | 35    |

| 2.4. Simulation Results                       | 37    |

| 2.5. Summary                                  | 44    |

| CHAPTER 3                                     | 45    |

| PERFORMANCE ANALYSIS OF UNDOPED AND GAUSSIAN- | DOPED |

| SURROUNDING-GATE MOSFET                       | 45    |

| 3.1. Introduction                             | 45    |

| 3.2. Structure Description                    | 45    |

| 3.3. Analysis                                 | 47    |

| 3.3.1. Undoped Body Surrounding-Gate MOSFET                                                | 47 |

|--------------------------------------------------------------------------------------------|----|

| 3.3.2. Gaussian Doping                                                                     | 50 |

| 3.4. Numerical Results and Discussion                                                      | 51 |

| 3.4.1. Undoped Body Surrounding gate MOSFET Analysis                                       | 51 |

| 3.4.2. Gaussian Doping Analysis                                                            | 58 |

| 3.5. Summary                                                                               | 61 |

| CHAPTER 4                                                                                  | 62 |

| PARAMETRIC ANALYSIS OF DOUBLE-GATE MOSFET<br>SURROUNDING-GATE MOSFET THROUGH EQUIVALENT CI |    |

| 4.1. Introduction                                                                          | 62 |

| 4.2. Model Formulation                                                                     | 63 |

| 4.2.1. Admittance Parameters                                                               | 63 |

| 4.2.2. Scattering parameters                                                               | 65 |

| 4.2.3. Gain Parameter Analysis for Amplifier Design                                        | 66 |

| 4.2.4. Capacitive model, operating as a switch                                             | 67 |

| 4.3. Simulation results                                                                    | 67 |

| 4.3.1. Double-Gate MOSFET                                                                  | 67 |

| 4.3.2. Surrounding-Gate MOSFET                                                             | 75 |

| 3.4. Summary                                                                               | 81 |

| Chapter-5                                                                                  | 82 |

| CONCLUSION AND FUTURE WORK                                                                 | 82 |

| 5.1. Conclusion                                                                            | 82 |

| 5.2. Future Scope                                                                          | 82 |

| REFERENCES                                                                                 | 84 |

## LIST OF TABLES

| Table 1. Milestones in the bulk technology [11].                         | 3  |

|--------------------------------------------------------------------------|----|

| Table 2. Scaling techniques [16].                                        | 9  |

| Table 3. The SCE [34].                                                   | 10 |

| Table 4. Limits of scaling [57].                                         | 14 |

| Table 5. The recent single chip transceivers for different applications. | 17 |

## **LIST OF FIGURES**

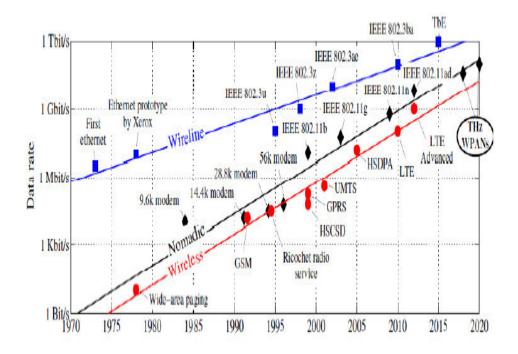

| Fig. 1.1 Edholm's law of data rates [1].                                              |

|---------------------------------------------------------------------------------------|

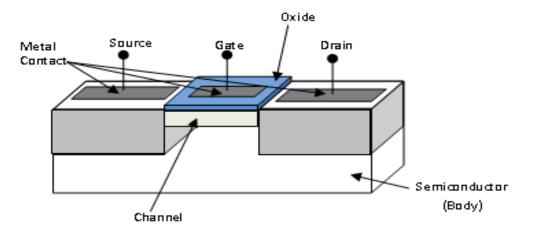

| Fig. 1.2 The four terminals MOSFET Structure.                                         |

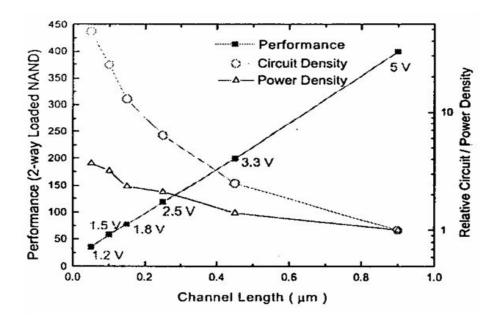

| Fig. 1.3 Trends for CMOS performance, power density and circuit density               |

| [18].                                                                                 |

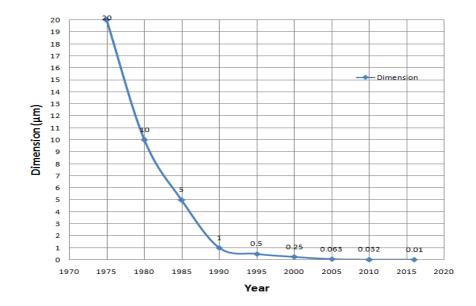

| Fig. 1.4 (a) Technology progress [22] (b) Semiconductor Technology Road Ma            |

| [Image source: ITRS update 2010].                                                     |

| Fig. 1.5 The schematic diagram of device scaling [16].                                |

| Fig. 1.6 Trend of MOSFET scaling [59].1:                                              |

| Fig. 1.7 The current-gain frequency variation over the years [ITRS 2011 update]       |

| 1:                                                                                    |

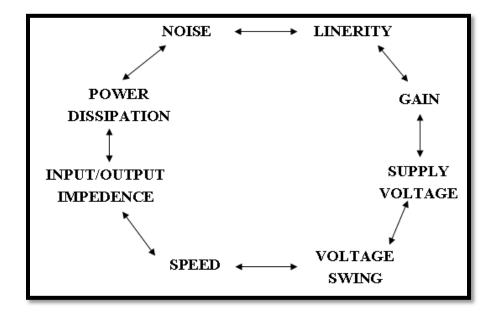

| Fig. 1.8 The analog octagon [64].10                                                   |

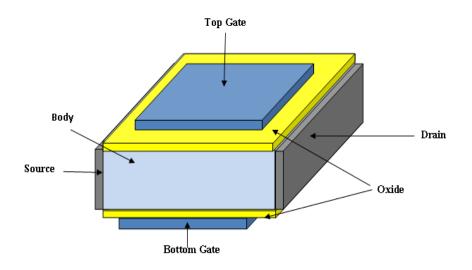

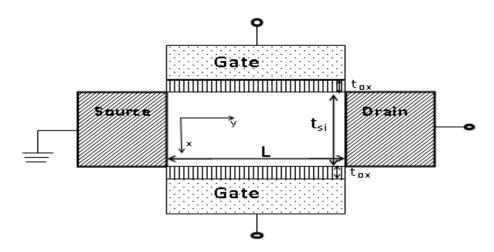

| Fig. 1.9 The Schematic of the double gate MOSFET.2                                    |

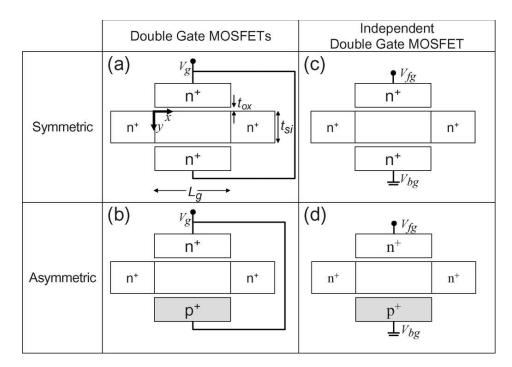

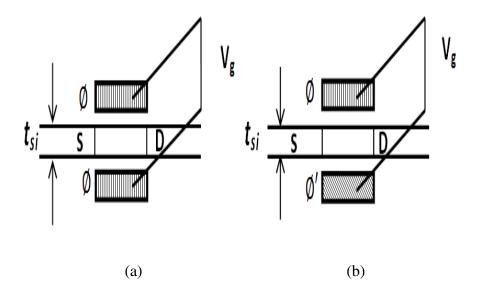

| Fig. 1.10 The schematics of DG MOSFET structure. (a), (b) tied gates and (c), (d      |

| separated gates. [86].                                                                |

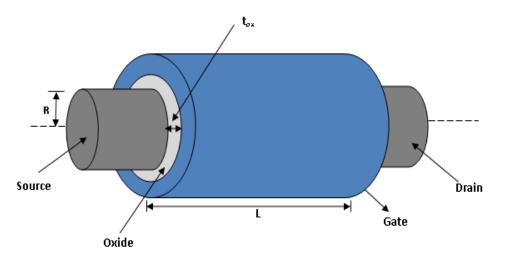

| Fig. 1.11 The Schematic of surrounding gate MOSFET.2'                                 |

| Fig. 2.1. Schematic of the DG MOSFET.32                                               |

| Fig. 2.2 (a) Symmetric Double Gate MOSFET, (b) asymmetric Double Gat                  |

| MOSFET. 3                                                                             |

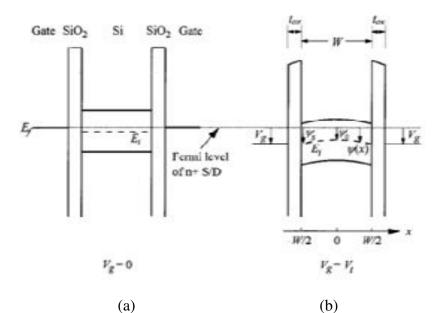

| Fig. 2.3 The band model of the symmetric DG MOSFET a) $V_{gs}=0$ V b) $V_{gs}=V_{ts}$ |

| [143]. 34                                                                             |

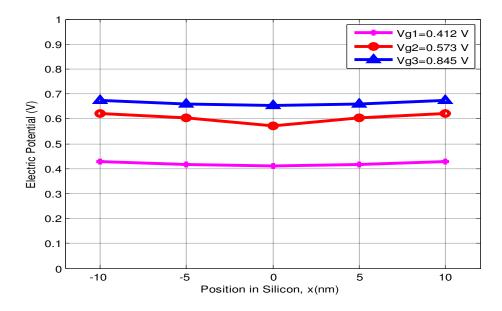

| Fig. 2.4 The electric potential at various positions in the silicon body thickness    |

| (nm) at different values of the gate-source voltages. 33                              |

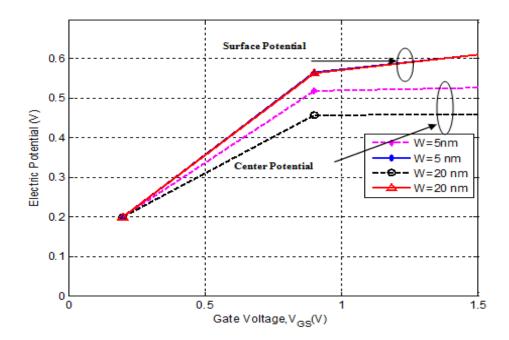

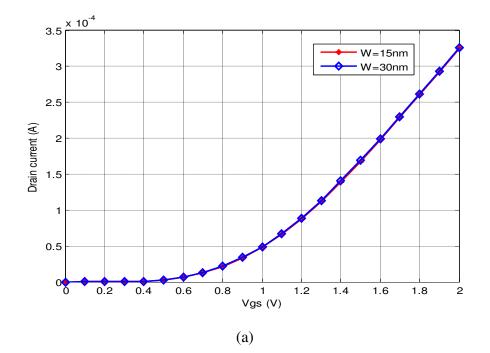

| Fig. 2.5 The potential versus gate-source voltage at different body width.38          |

| Fig. 2.6 The drain current characteristics of DG MOSFET at $t_{ox} = 2$ nm, $W = 30$  |

| nm and $L = 90$ nm with (a) input characteristics and (b) output                      |

| characteristics. 3                                                                    |

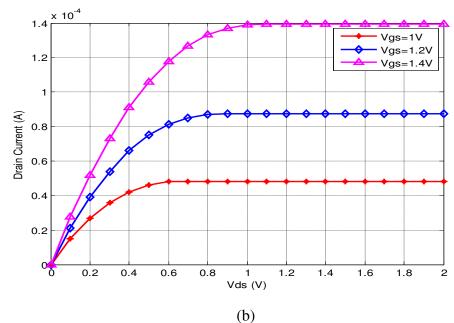

| Fig. 2.7 The response of gate-to-source voltage, over the drain current with $V_{ds}$ |

| 1V and $L = 90$ nm for different values of (a) device width with fixed $t_{ox}$ :     |

| 2 nm and (b) oxide thickness with fixed $W = 30$ nm. 40                               |

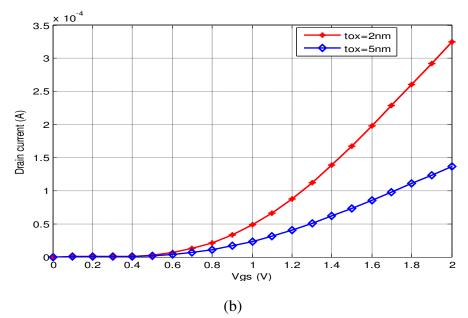

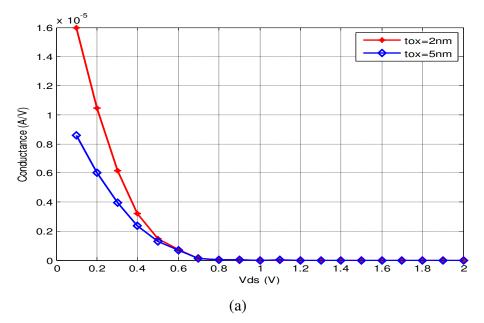

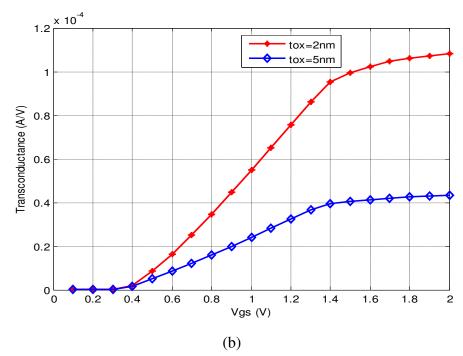

- Fig. 2.8 The effect of oxide thickness on the (a) conductance with  $V_{gs}$ = 1 V and (b) trans-conductance with  $V_{ds}$ = 1 V. 41

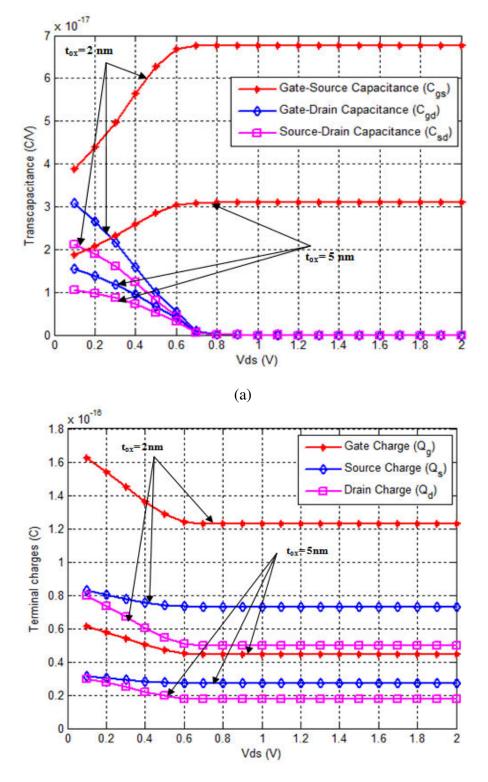

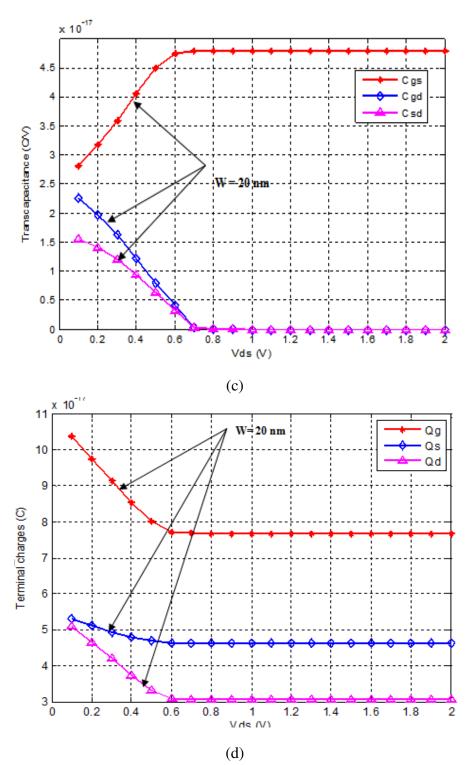

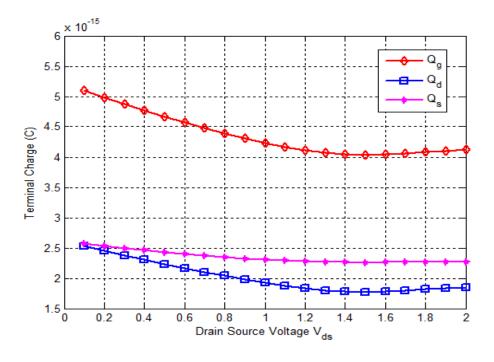

- Fig. 2.9 The response of the drain-to-source voltage on the (a) trans-capacitance, (b) terminal charges with W = 30 nm and L = 90 nm, (c) transcapacitance and (d) terminal charges with W = 20 nm,  $t_{ox} = 2$  nm and L = 90 nm at  $V_{gs} = 1$ . 43

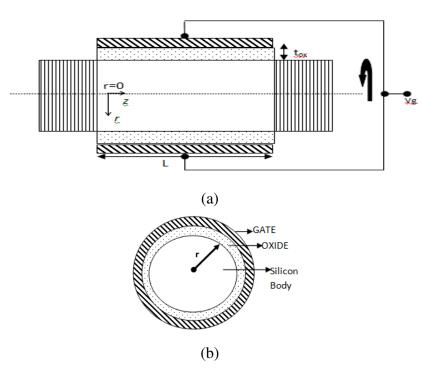

- Fig. 3.1 The surrounding gate MOSFET (a) 2-D longitudinal cross-sectional view and (b) horizontal cross-sectional view. 46

- Fig. 3.2 The energy band diagram of surrounding gate MOSFET (a) at  $V_{gs} = 0$  V and (b)  $V_{gs} = V_{th}$ . 46

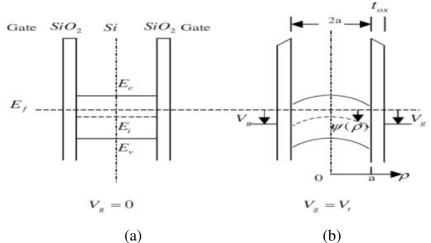

- Fig. 3.3 The potential versus radius of the cylinder (R) with different values of gate-to-source voltage ( $V_{gs}$ ). 52

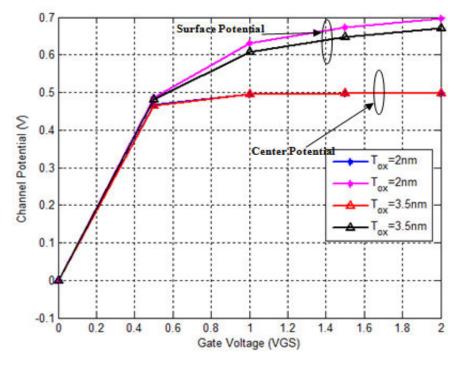

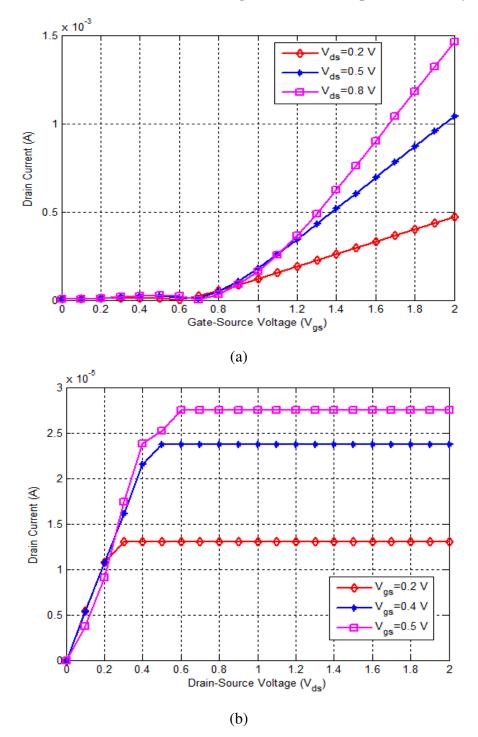

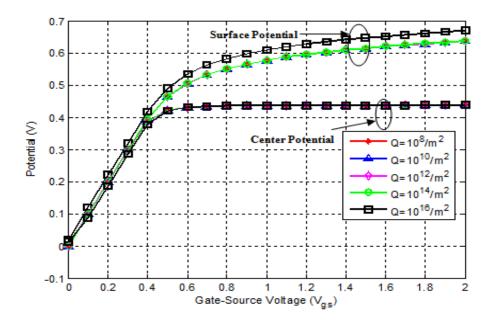

- Fig. 3.4 The response of the gate-to-source voltage  $(V_{gs})$  over surface potential and center potential with variation in the (a) oxide thickness  $(t_{ox})$  and (b) radius of the cylinder (R). 53

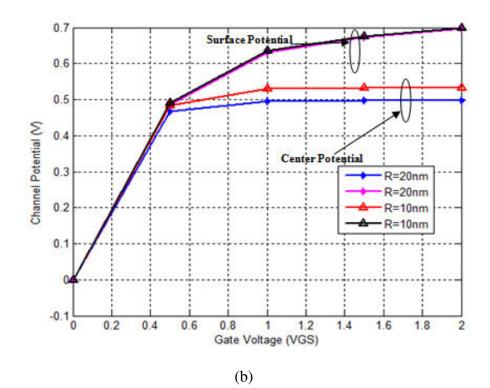

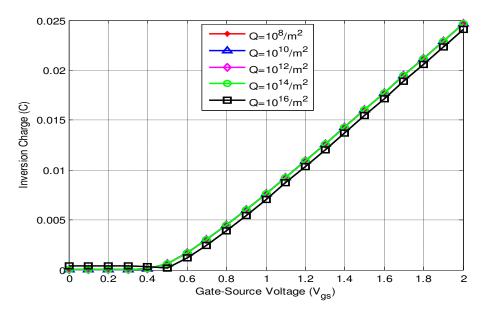

- Fig. 3.5 The response of gate-to-source voltage  $(V_{gs})$  over the inversion charge with the variation of (a) oxide thickness  $(t_{ox})$  and (b) radius of the cylinder (R). 54

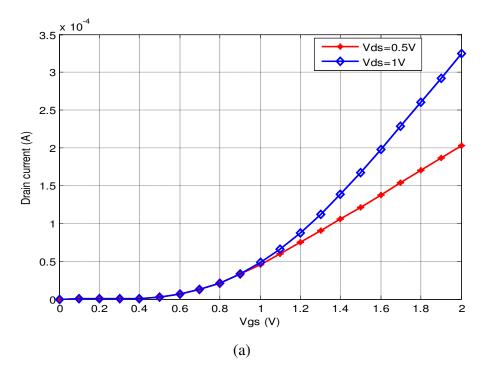

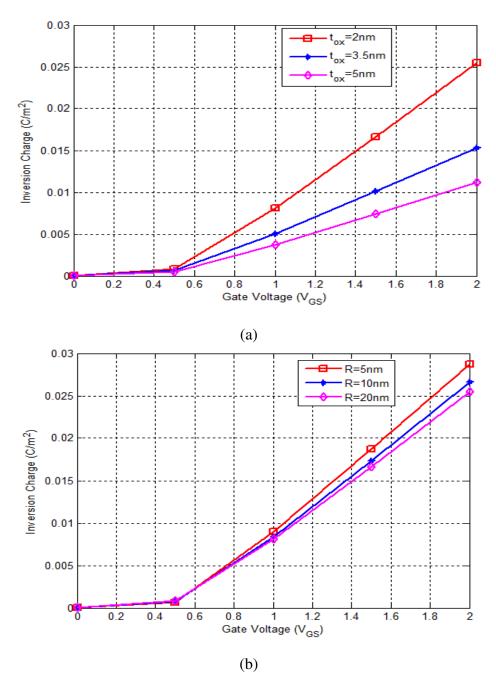

- Fig. 3.6 The drain current characteristics of the surrounding gate MOSFET with  $t_{ox} = 2 \text{ nm}, R = 20 \text{ nm}$  and L = 50 nm with the (a) gate-to-source voltage  $(V_{gs})$  and (b) drain-to-source voltage  $(V_{ds})$ . 55

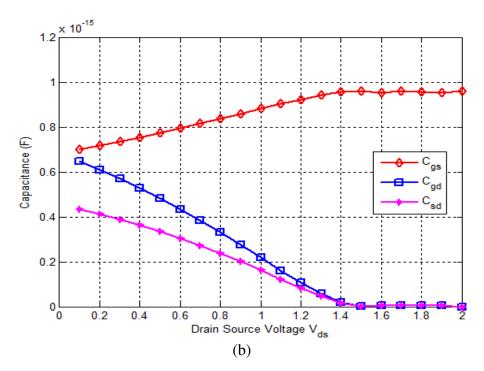

- Fig. 3.7 For the fixed  $V_{gs} = 2$  V the (a) variation of the charge with drain-to-source voltage, and (b) variation of the capacitance with the drain-to-source voltage. 57

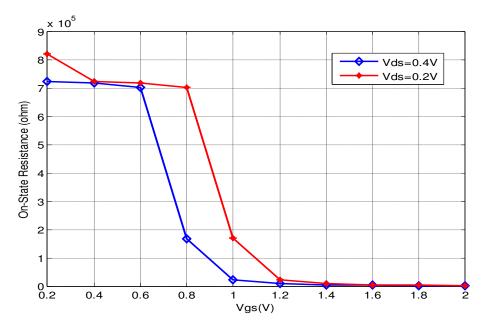

- Fig. 3.8 The on-state resistance versus gate-to-source voltage  $(V_{gs})$  for different drain-to-source voltage. 57

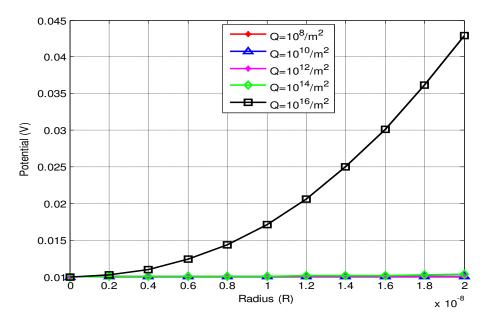

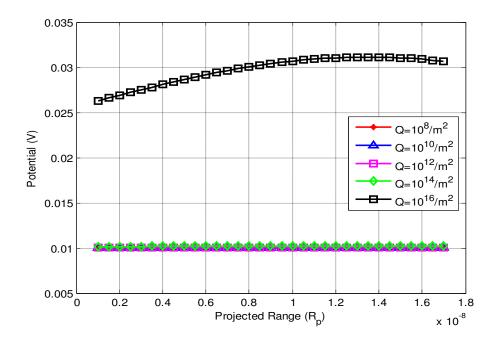

- Fig. 3.9 The variation of body potential across the radius of cylinder (R) with<br/>different implantation doses.58

- Fig. 3.10 The variation of body potential across the projected range  $(R_p)$  with different implantation doses. 59

- Fig. 3.11 The response of gate-to-source voltage  $(V_{gs})$  on the potential (center and surface) with different implantation doses (Q). 60

- Fig. 3.12 The response of gate-to-source voltage  $(V_{gs})$  over the inversion charge with different implantation doses. 60

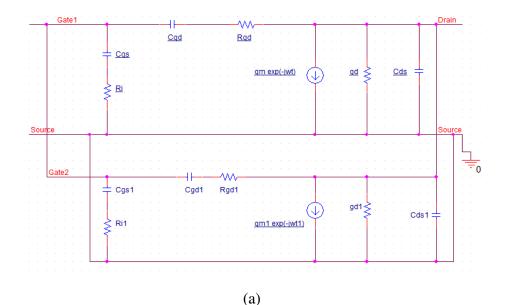

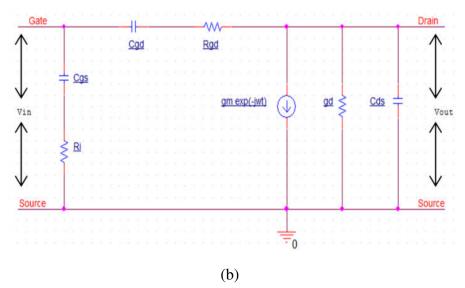

- Fig. 4.1 The small signal equivalent circuit model for the (a) double-gate MOSFET, and (b) surrounding-gate MOSFET. 64

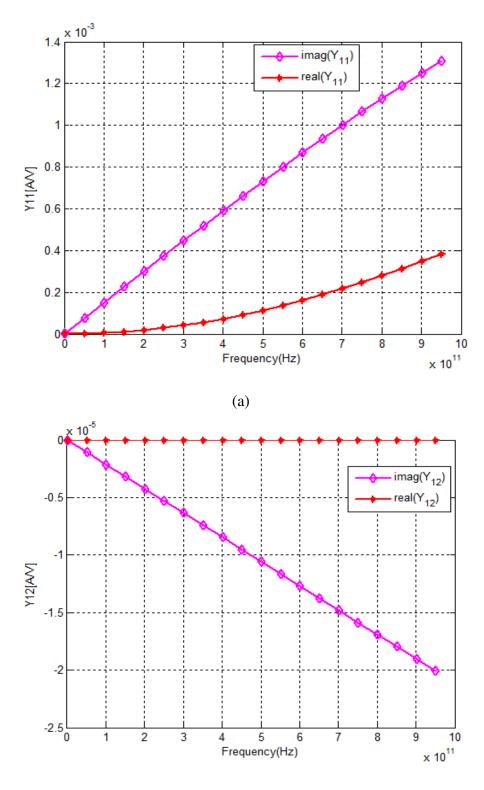

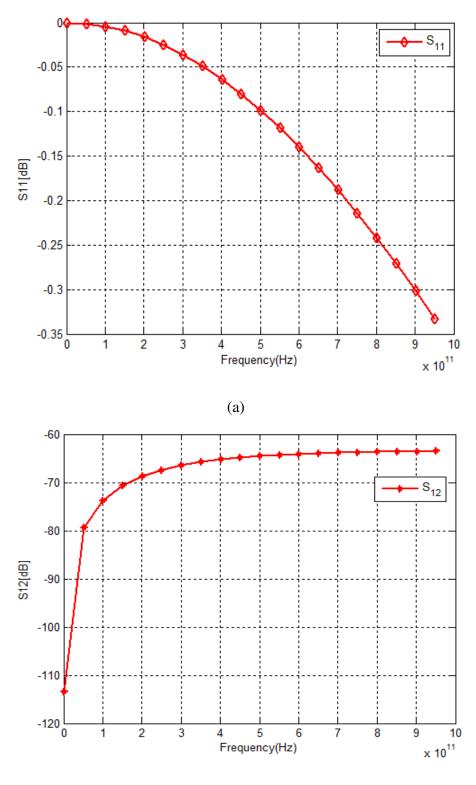

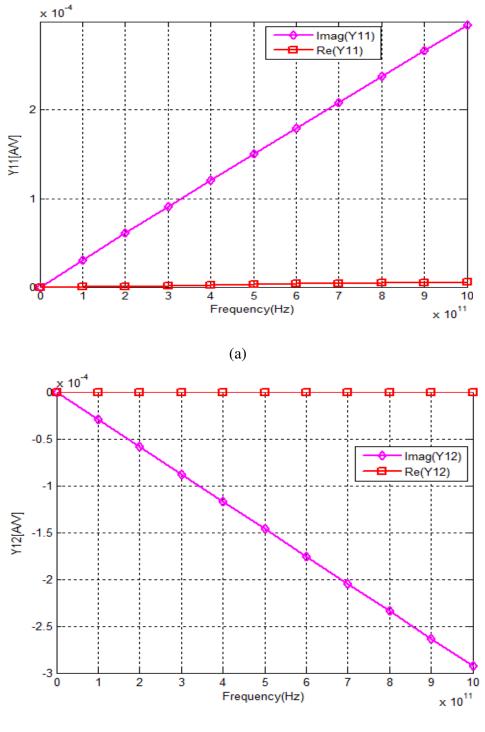

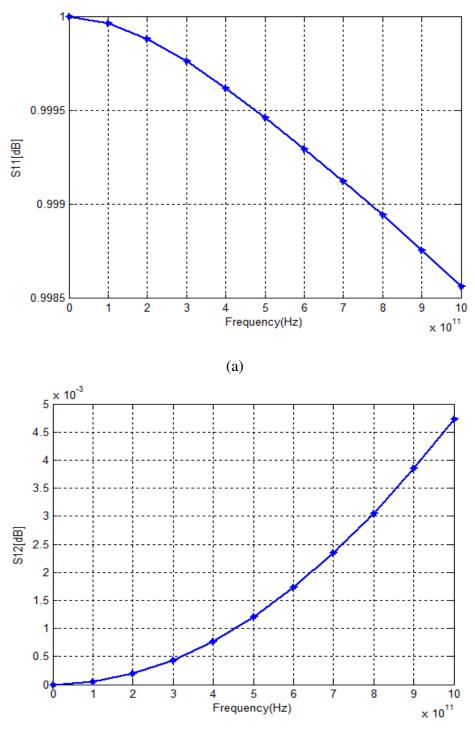

- Fig. 4.2 Y-parameters for DG MOSFET (a)  $Y_{11}$ , (b)  $Y_{12}$ , (c)  $Y_{21}$ , and (d)  $Y_{22}$ . 69

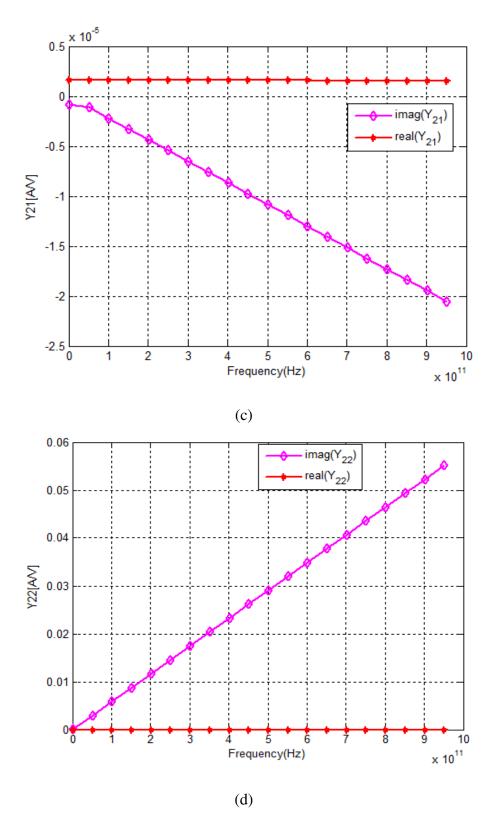

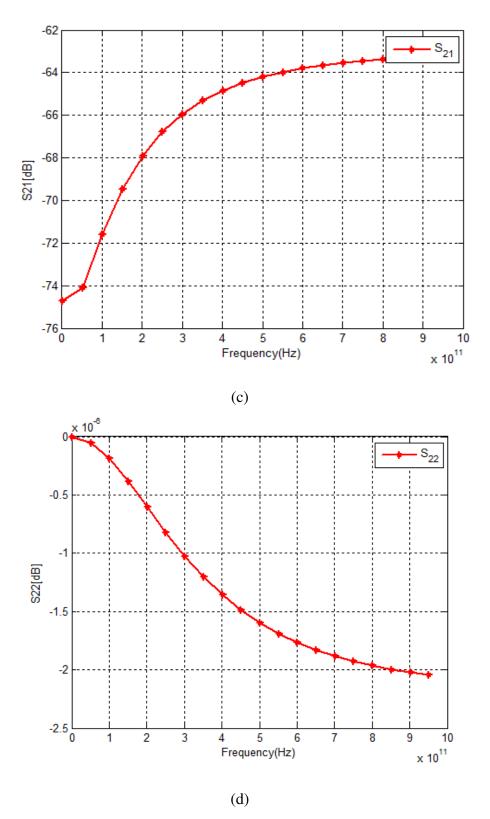

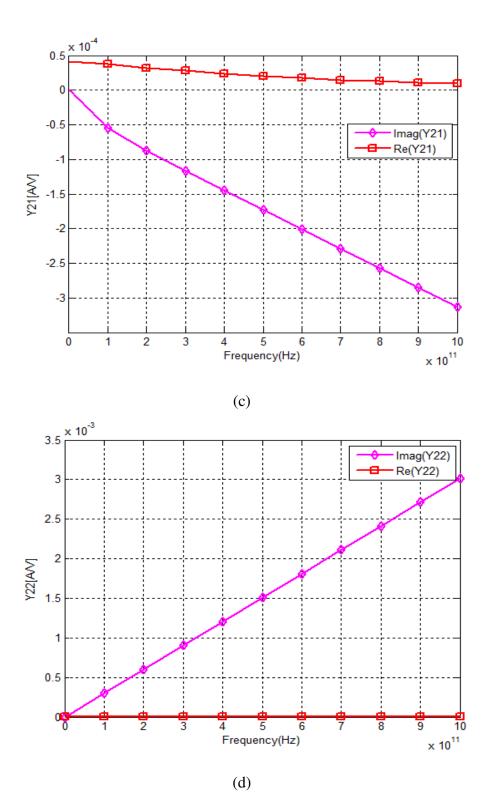

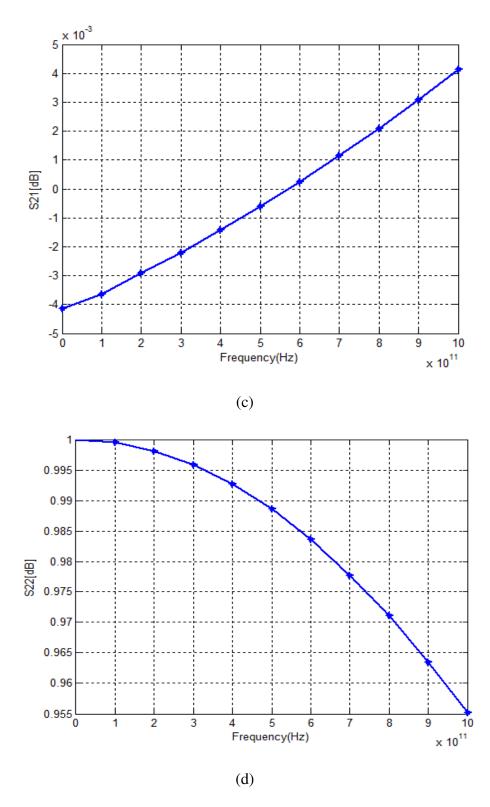

- Fig. 4.3 S-parameter analysis for DG MOSFET (a)  $S_{11}$ , (b)  $S_{12}$ , (c)  $S_{21}$ , and (d)  $S_{22}$ . 71

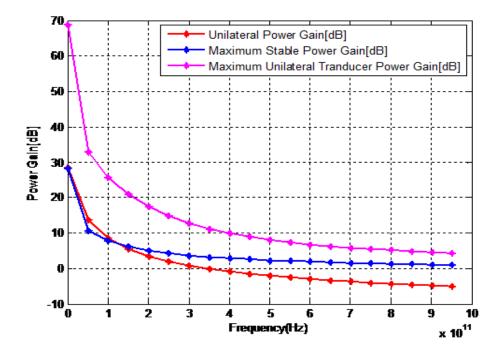

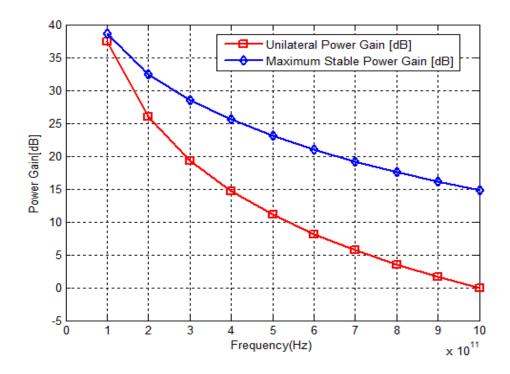

- Fig. 4.4 The power gain analysis of DG MOSFET. 72

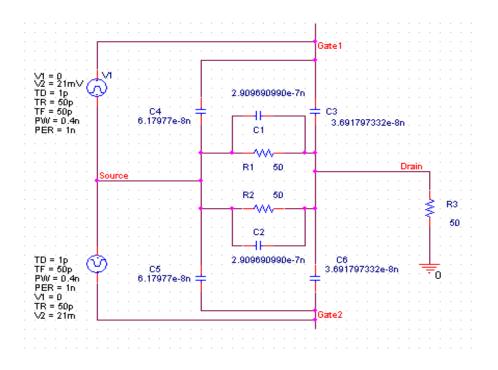

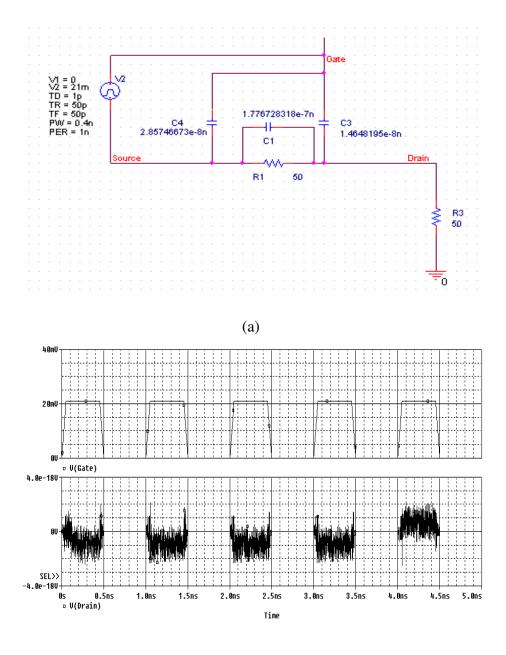

- Fig. 4.5 Design of DG MOSFET with SPICE (a) capacitive model, operating as an on-state switch, and (b) input signal applied to gates and output signal applied at the drain. 74

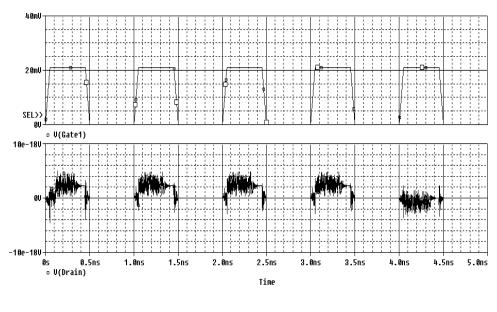

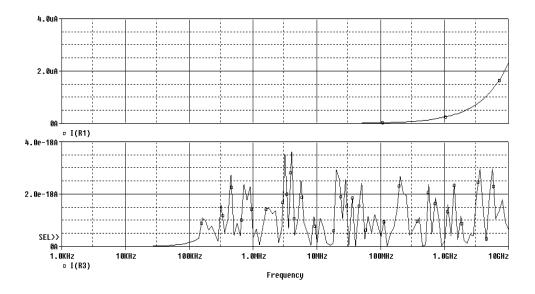

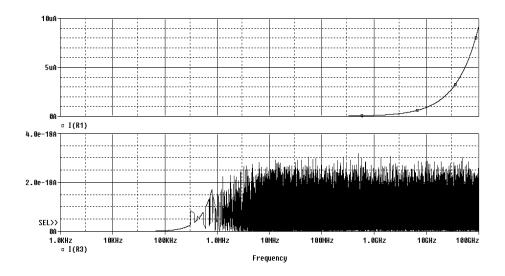

- Fig. 4.6 The source current and drain current variation when the AC signal applied to the DG- gate MOSFET. 74

- Fig. 4.7 Real and imaginary parts different Y-parameters of surrounding gate MOSFET (a) Y<sub>11</sub>, (b) Y<sub>12</sub>, (c) Y<sub>2</sub>, and (d) Y<sub>22</sub>. 76

- Fig. 4.8 S-parameter analysis of surrounding-gate MOSFET (a)  $S_{11}$ , (b)  $S_{12}$ , (c)  $S_{21}$ , and (d)  $S_{22}$ . 78

- Fig. 4.9 The power gain of surrounding-gate MOSFET. 79

- Fig. 4.10 Design of the surrounding-gate MOSFET with SPICE (a) capacitive model, operating as an on-state switch, and (b) input signal applied to gates and output signal applied at drain. 80

- Fig. 4.11 Source current and drain current variation when AC signal applied to the surrounding-gate MOSFET. 81

### LIST OF PUBLICATIONS

- Himangi Sood, and G. Singh, "A device for ultimate scaling and high frequencysymmetric double-gate MOSFET", International Journal of Electronics and Telecommunication (Under Review), April 2015.

- [2] Himangi Sood and G. Singh, "Performance analysis of undoped and Gaussian doped surrounding-gate MOSFET", Journal of Semiconductor (Under Review), May 2015.

# CHAPTER 1 INTRODUCTION

Over the last two decades, it is observed that every 18 months the wireless data rate doubles and are approaching the capacity of wired communication systems as can be seen in Fig. 1.1 [1]. In addition to this, till 2020 the data rate is reaching out to be greater than 1 Gbps.

Fig. 1.1 Edholm's law of data rates [1].

Therefore, to meet the requirement for the future wireless network, new technologies are needed which are having high data capacity and reduction in the overall power consumption of the system. Therefore, the THz range of frequency spectrum (from 300 GHz to 3000 GHz) can provide multiple GHz channel bandwidths. This spectrum provides the possibility to transmit at high data rate that is multi-gigabits per second. The recent research activities in THz technologies are increasing into much broader applications such as medical imaging, and wireless sensors and communications [2, 3]. Akyildiz et al [4] 1 | P a g e

discusses that the THz band communication will be addressing the capacity limitation of the current wireless communication system. Moreover, the other foremost requirements of the next generation communication system are the low power consumption and high processing speed, which should also be met in a much effective way.

In addition to this, the major key for enabling the effective wireless communication, networking is the radio frequency integrated circuits (RFIC). The analog designing and the high frequency designing techniques adds up to form RFIC design. Moreover, the analog designing is used at the low frequencies and the high frequency designing make use of the microwave theory where the concept of the transmission line is very important [5]. In addition to this, the higher frequency RF circuitry can be built by merging various forms of chips together and by using the same process as that for the traditional digital or baseband circuitry, that otherwise would be divided into multi-chip sets. However, single-chip integration also reduces the drawn current by reducing the number of off-chip loads that are necessary to drive multiple, non-integrated chipsets [6]. Moreover, the customer's requirements from RFIC design are the portability, universal, low power, multi-functionality, and miniaturization, which would further combine to reduce the overall cost of the of system on chip.

However, due to the reduced energy consumption of the MOSFET, they are seen to be the better option for ultra-fast communication [7]. Although, the designing of the device for the high frequency range a very crucial task, therefore new device structures are to be incorporated into the communication system that would provide the desired performance in the next generation communication system. However, Fujishima [8] demonstrated how low power and high speed communication for THz can be balanced. In addition to this, MOSFET has been an emerging device for RF/analog applications and the demand of the industry is encouraging for the replacement of the costly, huge sized and more power consuming devices with low power and high-density radio frequency devices. Before, moving on to the new device structures of MOSFET and the RFIC design performance parameters in the THz range, the next section is going to give a brief idea of MOSFET and tool used for the technology advancement.

#### **1.1. MOSFET**

Initially, the need for the smaller, cheaper, faster, less power consuming devices and as a replacement for the large sized vacuum tube encouraged Lilienfeld et al. [9] in 1930 to give the basic concept for Field Effect Transistor (FET) but was unable to demonstrate its structure due to the presence of the surface states at the interface of oxide and semiconductor that prevents the electric field from penetrating the semiconductor material. However, this problem was overcome by Kahng and Attala [10] who invented the first ever insulated gate FET by using the combination of three layers i.e. metal (M), oxide (O) and semiconductor (S). Moreover, the presence of the grown silicon dioxide layer on semiconductor surface reduces the amount of surface states initially present and gave the name MOSFET (Metal Oxide Semiconductor Field Effect Transistor).

| Year | Technology                 | Channel Length (um) |

|------|----------------------------|---------------------|

| 1960 | MOSFET                     | -                   |

| 1969 | Ion-implanted channel      | -                   |

| 1971 | Intel 4064 Microprocessor  | 10                  |

| 1979 | Silicided polysilicon gate | 1                   |

| 1986 | Retrograde channel doping  | 0.5                 |

| 1993 | Copper interconnect        | -                   |

Table 1 Milestones in the bulk technology [11].

Several milestones in bulk technology as very effectively summed up by Wong et al [11] as shown in Table 1 starting from the invention of MOSFET in 1960, the production of ion-implanted channels, with further the invention of the first Intel 4064 microprocessor. The author [11] has also pointed out other advancements such as the silicided polysilicon gate to retrograde channel doping and the use of the copper interconnect which further increase the performance parameters, i.e. increases drain current, reduces the leakage current, of the MOSFET.

Since then, a MOSFET is used as a fundamental switching device with four terminals as shown in Fig.1.2 (Gate, Drain, Source and Body) in very large scale integrated (VLSI) circuit that is controlled by the electric field applied to one of the terminal that is a gate.

Fig.1.2 The four terminals MOSFET Structure.

Moreover, the terminals drain, source and gate are highly doped, but the body is lightly doped. The gate electrode is made of metal or poly-silicon and is separated from silicon body with a thin insulating film which acts as an energy barrier between the gate electrode and silicon body. The conductive region of the device may either be p-type or n-type depending upon the application. However, with proper bias condition a significant current can flow between the source and drain terminals of the MOSFET which makes the possibility of two types of current flow in the device: 1) Diffusion current which is the dominant current when applied gate voltage is less than the threshold voltage and 2) Drift current which is dominant when the applied gate voltage is greater than that of the threshold voltage. On the basis of the flow of current between the drain and source, three operating regions are feasible [12-14]:

- Cutoff region, where no current flows excluding sub-threshold current which become dominant when the dimensions of the device becomes significantly smaller,

- Linear region, where the linear current flows between source and the drain terminals, and

- 3) Saturation region, where the current gets saturated as the channel formed between the source and drain is pinched off at the drain side.

#### 1.2. Scaling

To improve the system reliability, current drive, computational capability and integration density at lower cost, scaling should be applied [15]. The basic idea behind scaling [16, 17], lies in to produce smaller transistor with performance similar to that of the larger one and simultaneous reduction of all the dimensions. However, the geometrical ratio, (the ratio between the horizontal dimensions (channel width) to that of the vertical dimension (channel length)) should be maintained with precision.

Fig. 1.3 Trends for CMOS performance, power density and circuit density [18].

Moreover, with the use of scaling, the reduction in the delay and further the advancement in clock frequency are seen. In addition to this, device density is doubled and reduction in energy and the active power per transition is also reported [18]. However, Fig. 1.3 also shows the linear circuit performance due to the technology scaling.

(b)

Fig. 1.4 (a) Technology progress [22] (b) Semiconductor Technology Road Map [Image source: ITRS update 2010].

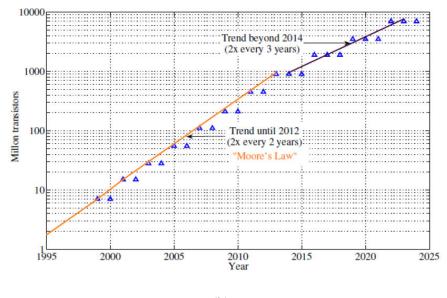

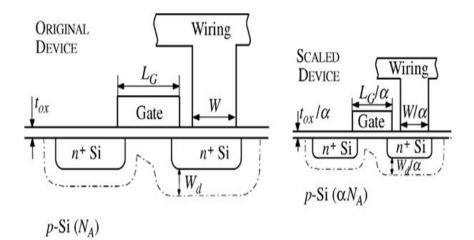

Therefore, the semiconductor industry was encouraged to project the scaling theory in addition to the observation made by Gorden Moore [19, 20], in the form of International technology Roadmap of Semiconductor (ITRS) [21]. Fig. 1.4 (a) forecasts the dimension reduction over the year through the ITRS roadmap, and Fig. 1.4 (b) suggests till 2014 the doubling of transistors will follow Moore's law, after that the pace of advancement (i.e. doubling) will slow down to every 3 years. Fig. 1.5 suggests the conceptual idea for scaling, were *a*, *W*, *W*<sub>d</sub>, *L*<sub>g</sub> and *t*<sub>ox</sub>, represents the scaling factor, wiring width, depletion depth, gate length and oxide thickness respectively.

Fig. 1.5 The schematic diagram of device scaling [16].

However, based on the idea the classical scaling techniques can be classified into two types: [14]

- 1) Constant voltage scaling and

- 2) Constant field scaling.

In the constant voltage scaling [23], all the dimensions of device are scaled-down keeping the power supply voltage and terminal voltages unchanged so as to remain compatible to prevailing electronic system regarding supply voltage standards. However, this scaling technique is not a practical one, as the power dissipation increases to a high level which leads to the electro-migration, hot carrier degradation and oxide breakdown [24]. Moreover, in the constant field

scaling introduced by Dennard et al. [16], all the voltages and the dimensions are scaled down, while doping as well as current densities are increased by the scale factor  $\alpha$ , keeping the vertical field constant. In addition to this, the speed of circuit is also enhanced by the same factor  $\alpha$  and circuit density increases by  $\alpha^2$ , however, the problem arises when the horizontal field keeps on increasing as the dimension of device become significantly smaller, creating problems on the potential barrier at the source end [25]. Also, the voltages, sub-threshold slope and off-current are not scaled well as the length scale down, which violates the constant field scaling technique [26]. Therefore, Baccarani et al. [27] has proposed more generalized scaling technique in which the vertical and horizontal fields are changed by the same multiplication factor. Although, the shape of electric field is preserved now, it has potential issue such as significant enhancement in the power density. Brews [28, 29] also proposed a scaling method called sub-threshold scaling which does not stress on specific factor for scaling individual dimensions and allows independent manipulation of a large number of variables as long as the remaining variables compensate for these changes. The summary of these scaling is shown in Table 2.

However, the above mentioned scaling techniques only tell about how to shrink the device, it does not tell anything about the limit of the scaling. There are certain physical phenomenon's which limit these scaling techniques such as quantum mechanical tunneling, that happens as the barrier existing in MOSFET becomes very thin and the random dopant fluctuation, due to the present manufacturing techniques.

In addition to this, the power supply scaling also has a limit which is the thermal voltage [30]. The Si band-gap potential ( $E_g/e$ ) is also the major parameter which cannot be scaled down, and as the supply voltage is scaled down the effect of band-gap potential increases which results in increase in electric field and the depletion depth. Here, the band gap potential can only be changed by changing the semiconductor itself. As the electric field increases, it confines more charge carrier closer to the surface, which further reduces the mobility, increases the

quantum confinement energy and the gate depletion, consequently the threshold voltage is increased.

| Physical<br>parameter                     | Constant Electric<br>Field Scaling<br>Factor | Generalized<br>Scaling Factor | Generalized<br>Selective<br>Scaling Factor |

|-------------------------------------------|----------------------------------------------|-------------------------------|--------------------------------------------|

| Channel length,<br>Insulator<br>thickness | 1/α                                          | 1/α                           | $1/\alpha_d$                               |

| Channel width                             | 1/α                                          | $1/\alpha$                    | $1/\alpha_{\rm w}$                         |

| Electric Field                            | 1                                            | ¢                             | E                                          |

| Voltage                                   | 1/α                                          | $\epsilon/\alpha$             | $\epsilon/\alpha_d$                        |

| On-current                                | 1/α                                          | $\epsilon/lpha$               | $\epsilon/lpha_{ m w}$                     |

| Doping                                    | А                                            | εα                            | €α <sub>d</sub>                            |

| Area                                      | $1/\alpha^2$                                 | $1/\alpha^2$                  | $1/{\alpha_w}^2$                           |

| Capacitance                               | 1/α                                          | 1/α                           | $1/\alpha_{\rm w}$                         |

| Power<br>dissipation                      | $1/\alpha^2$                                 | $\epsilon^{2\prime}\alpha^2$  | $\epsilon^2/\alpha_w \alpha_d$             |

Table 2 Scaling techniques [16].

Moreover, several methods are utilized to reduce the threshold voltage, i.e. retrograde doping profile and the body biasing relative to source etc [31, 32]. Therefore, there is a need of proper selection of power supply voltage and threshold voltage [33].

While it is widely believed that CMOS will still be the dominant technology in the near future, practical and fundamental limits of CMOS scaling poses tremendous challenges beyond the 45nm technology node. In addition to this the major challenge faced by the circuit designers is the Short channel effects (SCE).

### **1.3. Short Channel Effects**

When the MOSFET channel length that is the distance between source and drain in the MOSFET, is comparable to the depletion depth of the source and drain under a gate with zero drain-source voltage, the device is considered to be short. As the dimension of device shrinks significantly more, the short channel effects (SCE) dominates over the device performance [34] and attributes following two physical phenomena:

- 1) The restriction imposed on electron drift characteristics in the channel, and

- 2) Alteration of the threshold voltage due to short channel length.

The Table 3 summarizes the various short channel effects.

| S.No | Effect                                         | Reason                                                                                                                                                                                                                                                             | Reference |

|------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1.   | Drain induced<br>barrier<br>lowering<br>(DIBL) | As the drain voltage increases, the potential barrier of the channel decreases and allows the flow of electrons between the source and drain even if the gate voltage is lower than that of the threshold voltage.                                                 | [35-37]   |

| 2.   | Surface<br>scattering                          | The electric field component in the<br>direction of current flow increases due<br>to the extension of the depletion layer<br>in the channel which further makes the<br>surface mobility field dependent as the<br>channel length becomes significantly<br>smaller. | [38-39]   |

| Table 3 | The | SCE | [34]. |

|---------|-----|-----|-------|

|---------|-----|-----|-------|

| 3. | Velocity<br>saturation            | For a short channel device, the current<br>saturates because of the carrier<br>velocity saturation in place of pinch-<br>off point in bulk MOSFET and current<br>is independent of gate-to-source<br>voltage which happens when the<br>dimensions of device are scaled down<br>without lowering the voltages,<br>therefore the trans-conductance<br>reduces in the saturation-mode of<br>operation. | [40-41] |

|----|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 4. | Hot electron<br>effect            | As the high energy electrons enter the<br>oxide they are trapped, which giving<br>rise to oxide charging that accumulate<br>with time and degrade the device<br>performance by increasing threshold<br>voltage and affect adversely the gate's<br>control on the drain current.                                                                                                                     | [42-43] |

| 5. | Threshold<br>voltage roll-<br>off | As the field pattern generated by the gate is 2-D for short channel devices because of closeness of source and drain, the threshold voltage varies with the channel length. The part of the channel is already depleted, therefore significantly less voltage is required for the operation of MOSFET as the threshold voltage decreases.                                                           | [27]    |

| 6. | Punch-                            | Due to the proximity of drain and                                                                                                                                                                                                                                                                                                                                                                   | [44]    |

|    | through                                 | source, the depletion region of the<br>drain and source extend into the<br>channel and merge. Therefore, the<br>current flow between the source and<br>drain which cannot be controlled by<br>the applied gate bias.                                                                                                                                                                                                                                                                                            |         |

|----|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7. | Oxide<br>tunneling<br>current           | As the oxide thickness reduces the electric field increases, which further forces the current to flow in the gate terminal.                                                                                                                                                                                                                                                                                                                                                                                     | [45-46] |

| 8. | Reverse short<br>channel effect         | The retrograde doping profile results in<br>point defects at the surface edge where<br>the impurity atoms pile up and<br>increases the channel doping closer to<br>the source/drain region. For the short<br>channel devices the region with the<br>enhanced doping is a significant part of<br>the channel. Therefore, the increase in<br>doping in addition to the reduced<br>channel length causes the threshold<br>voltage to increase with scaling until<br>eventually short channel effects take<br>over. | [47]    |

| 9. | Gate induced<br>drain leakage<br>(GIDL) | The electric field due to the drain can<br>cause the overlap region to form a<br>depletion region and if this field is<br>significantly high it may invert the<br>surface to p-type. When the channel is<br>being formed the carriers are swept in                                                                                                                                                                                                                                                              | [48-49] |

|     |                         | this p-well. The effect of the increase<br>in the oxide thickness is more<br>significant to GIDL as compared to<br>that of the gate length.                                                                                                                                                                                                                                                  |         |

|-----|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 10. | Mobility<br>degradation | For the short channel devices, one<br>reason for the decrease in mobility is<br>the velocity saturation, which occurs<br>due to the presence of electric field<br>perpendicular to the gate. The<br>electrons slow down by the increase in<br>scattering, thereby decreasing the<br>mobility with respect to the bulk<br>MOSFET. Also, as the surface is<br>rough, more scattering is there. | [50-51] |

However, the reduction of SCE is of prime concern while maintaining the better device performance in nano-scale regime. Therefore, several methods have come up with some negative effects such as performance degradation and additional leakage. The increase in channel doping so that the electric field lines that originate from the drain and propagate to the source are terminated, however, this high level of doping degrades the low field mobility of the carrier as the impurity scattering is increased, which further reduces the drive current [52]. Moreover, it also increases the gate-induced drain leakage (GIDL) and band-to-band tunneling across the reverse-biased drain junction. In addition to this, the significantly more threshold voltage variation is observed due to the statistical fluctuation of channel dopants, mainly in the nano-scale regime [53]. The reduction of oxide thickness is important for improving the gate control on the channel, however, this causes tunnelling and results the leakage current when the thickness of the oxide reaches 2 nm and further increases standby power [54, 55, and 31]. However, with the lowering of source/drain junction depth to reduce drain coupling to the source

barrier, the doping density has to be increased, however this doping density has an upper limit for solid solubility. Therefore, the series resistance increases and degrade the device performance [56]. Table 4 suggests the certain scaling limits which introduce additional problems of short channel effects (SCE).

| Feature         | Limit             | Reason                       |

|-----------------|-------------------|------------------------------|

| Oxide thickness | 2.3 nm            | Leakage(I <sub>off</sub> )   |

| Junction Depth  | 30 nm             | Resistance(R <sub>sd</sub> ) |

| Channel Doping  | $V_{th} = 0.25 V$ | Leakage(I <sub>off</sub> )   |

| Channel Length  | 0.06 µm           | Leakage(I <sub>off</sub> )   |

Table 4 Limits of scaling [57].

Moreover, by the scaling the dimension the MOSFET the processing speed can be enhanced and further improve RF performance. The important metrics for RF MOSFET circuits are the maximum oscillation frequency and cut-off frequency. The former is defined as the frequency at which the current gain of the device becomes unity and later defines the frequency at which power gain becomes unity. However, both these metrics relate to the trans-conductance and parasitic capacitance. As the dimension of the device reduces, the cutoff frequency of the device increases to up to 400 GHz. Noise figure is also one of the other important figure-of-merit. However, Song et al [58] have purposed a new figure-of-merit for low noise amplifier and also predicted the close optimum gate voltage to maximize this figure of merit.

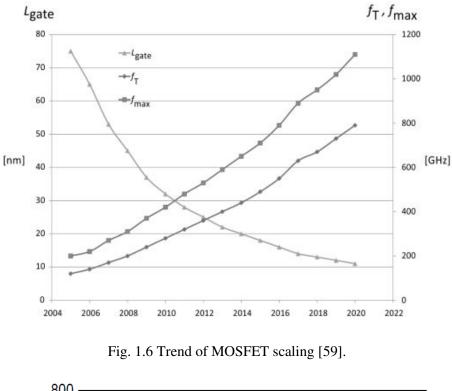

Therefore, Fig. 1.6 shows the advances in MOSFET technologies which have continued, with further increase in the cutoff frequency ( $f_{\rm T}$ ) of the devices [59]. Moreover, due to relatively high  $f_{\rm T}$  values, the bulk-silicon MOSFET device is becoming a viable technology choice in the analog and RF applications for portable wireless communication systems.

Fig. 1.7 The current-gain frequency variation over the years [ITRS 2011 update].

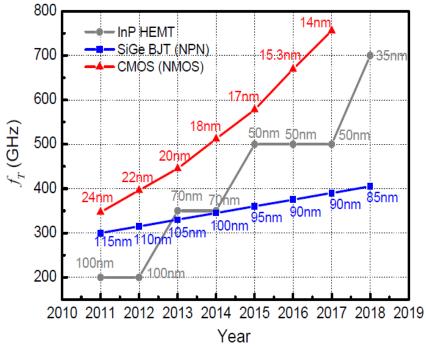

However, it can also be seen through Fig. 1.7 that a high value of the current gain frequency can be achieved with the CMOS technology. However, with 18 nm

technology, the  $f_{\rm T}$  is achieved to be is 511 GHz, which shows that the CMOS has an advantage for high speed applications in future communication system.

In addition to this, the low power dissipation of the device is required for the applications such as battery operated single-chip typical wireless transceiver [60], which can be achieved by reducing the device supply voltage. Therefore, the communication market has reached a revolutionary era with the various forms of improvement in the MOSFET structure. Moreover, the circuits formally implemented as a discrete structure, now, which is implemented on the single chip. Therefore, the system on chip is no longer a mere idea. Due to the high unity gain of MOSFET, it becomes an attraction for the RFIC circuit designers [61]. However, it is observed that, the MOSFET must be operated in the moderately inverted region to achieve the desired circuit performance in ultra low power RFIC design [62]. In addition to this, Lee and Cheng [63] have analyzed the MOSFETs, which has higher low-frequency limit (LFLs) as compared with BJTs which is useful for RFIC design as well as generating HF distortion model for MOSFETs and recently new technologies acting as a driving force in the personal wireless communication market.

Fig. 1.8 The analog octagon [64].

However, Razavi [64] has shown the difficulty in using the digital MOS technology for the analog application, that is only one trade-off is optimized, i.e. power-speed trade-off, although a multidimensional design space in the form of the octagon as shown in Fig. 1.8 is presented where every parameter trade-off with each other. For example, to lower the noise of a front-end amplifier, we must consume a greater power or sacrifice linearity or to increase the gain of the amplifier, we have to work on high supply voltage or sacrifice linearity. In addition to this, if the supply voltage is reduced, power dissipation may increase. Woerlee et al [65] have confirmed the higher potential of CMOS for RF applications at GHz frequency.

| S. No | Technology | Application                                                                        | Reference |

|-------|------------|------------------------------------------------------------------------------------|-----------|

| 1.    | 0.090 µm   | 5 Mbps transceiver with energy<br>harvesting module for wireless sensor<br>network | [66]      |

| 2.    | 0.18 µm    | 2.4 GHz low rate wireless personal area network (WPAN)                             | [67]      |

| 3.    | 0.090 µm   | 2.4 GHz low power Zigbee transceiver                                               | [68]      |

| 4.    | 0.028 µm   | Phase modulated continuous wave radar at 79 GHz                                    | [69]      |

| 5.    | 0.13 µm    | 24 GHz UWB transceiver with self organizing localization network                   | [70]      |

| 6.    | 0.13 µm    | 3-10 GHz front-end transceiver used for low power biomedical radar                 | [71]      |

Table 5 The recent single chip transceivers for different applications.

Recently, many transceiver chips using the CMOS technology has been developed, as summarized in Table 5. Moreover, the reduction of feature size of the device based on the channel, and gate engineering [35] also introduces additional parasitic and new phenomenon such as SCE, parasitic source/drain resistance, poly-silicon depletion layer effect, ballistic transport, carrier energy quantization, bias dependent parasitic capacitances etc. As the fabrication processes also limits the scaling, novel techniques have to be introduced to keep the pace with the scaling to yield the desired throughput, and to retain the progress in device scaling technology.

To move forward in the direction to achieve better performance, novel material and device structures, which are the non-conventional structures, are required beyond 65nm technology [72]. Moreover, Rue et al [73] analyzed that the output power capability of the transmitter will degrade as the device will scale down due to the hot-carrier injection and reducing the oxide will not be effective. Therefore, the innovated device structures can reduce the short channel effects (SCE), therefore they would be a better choice to be used in the future transceiver chips, which are discussed in the following section.

#### **1.4. Advanced MOSFET Structures**

In the silicon-on-insulator (SOI) technology, the presence of buried oxide layer below the transistor junction reduces the junction capacitances and reverse body effect, which provides a faster and less power consuming device, has been considered as one alternative to the conventional bulk MOSFET which offer performance as expected from the next generation Silicon technology [31]. Moreover, by using the buried oxide layer the fringing capacitances are suppressed, that provides better processing speed [74]. However, the fullydepleted MOSFET improves the short channel effect (SCE), transistor scalability and circuit performance [75, 76]. The introduction of ultra-thin SOI technology offers the significant advantage of reducing the leakage paths by stopping the penetration of the drain electric field in the source region. However, this device

suffers from degradation in the on-state current due to mobility degradation and increase the external resistance, which can be rectified by the use of the thin gate spacer with raised source/drain process. In addition to this, the threshold voltage control with the use of doping is difficult, therefore the poly-silicon gate is replaced with a metal silicide gate where it is controlled by the work function engineering by the gate. Moreover, the mobility degradation due to the surface roughness is still an issue when the body thickness reaches up to 5 nm [77]. For fully depleted SOI MOSFETs, the drain electric field penetrates though the buried oxide into the channel region, thereby resulting in a large impact on the channel electrostatics. However, the bulk MOSFETs and DG MOSFETs can achieve better short-channel effect compared to that of the fully depleted SOI MOSFETs due to the screening of the channel by the bottom layer. Therefore, with the advantages of high processing speed, lower power dissipation and consumption, high tolerance to radiations and low value of parasitic capacitances, some other unavoidable issues come into picture when the SOI dimension reaches to nanometre regime [75].

To seek possible alternatives for bulk MOSFETs beyond the 45nm technology node, a number of novel multi-gate MOSFETs have been proposed, including Surrounding Gate, Pi-Gate [78], Omega-Gate [79], Tri-Gate [80] and Double-Gate (DG) MOSFETs. Various numerical simulations and analytical analysis have shown better scalability of multi-gate MOSFETs over the bulk MOSFETs. The improved scalability allows multi-gate MOSFETs to scale down to shorter gate length with the same off-current or produce less off-current with same gate length, thereby achieving better power-speed product. Among these new emerging devices, the DG MOSFET is most promising because of its compatibility with the conventional planar technology. In addition to this, DG MOSFET reduces the fringing field through drain-to-body which further improves the device scalability, and the mobility requirement in this structure is less as compared to the bulk MOSFET due to less vertical field. However, the mobility can be enhanced by using the following techniques: 1) strain engineering and 2) orientation effects [81]. Therefore, more enhanced versions of SOI structures come into the picture, which is a thin body fully-depleted SOI MOSFET, raised source and drain fully-depleted SOI MOSFET, metal source and drain fully-depleted SOI MOSFET and multiple-gate fully-depleted SOI MOSFET. Recently, to advance the scaling of MOSFET technology the double-gate MOSFET and surrounding gate MOSFET using lightly doped and ultra-thin body layer is an emerging research area [82]. Moreover, for the advancement in the technology in the wireless communication field, the standard MOSFET structures using the standard CMOS technology should be replaced by more innovative structures such as double-gate MOSFET and surrounding-gate MOSFET. The advantages of these structures for the operation in the high frequency regime of spectrum are discussed in the following section.

#### **1.4.1. Double Gate MOSFET**

The main design objectives of DG MOSFET are: 1) to reduce SCE and 2) to maintain good electrical characteristics [83]. The planer DG MOSFET is an extension of the single gate MOSFET that consists of two gates designated as a front-gate and back-gate, within which the ultra thin silicon layer is sandwiched [84]. The additional gate significantly increases the electrostatic gate control over the channel and these gates are effective in shielding the drain electric field-lines from reaching the source to reduce the potential barrier as well as reducing the SCE. Due to un-doped/lightly doped body, the problem of random dopant fluctuation is also absent. Moreover, both the gates contribute to inversion carriers, which have high drive capability and two channels for the current flow are formed, when these two gates simultaneously control the charge. In addition to this, as the silicon film is very thin there exists a good coupling between the front and back gate, which affect the terminal characteristics of the MOSFET. Fig. 1.9 shows the schematic of DG MOSFET.

In the common mode operation, both the gates are switched simultaneously, however for other possible mode of operation, a back gate bias is applied to create

a conducting plane, and switch the front gate which provides an additional parameter for the circuit design. Therefore, two types of structures are possible:

- Symmetric DG MOSFET (SDG MOSFET): Both the gates have identical work function. However, the threshold voltage can be adjusted with the help of work function of gates. The thin silicon substrate is under volume inversion condition, therefore the conduction of carriers is across the entire volume of material as compared to that of the bulk devices.

- Asymmetric DG MOSFET (ADG MOSFET): Both the gates have different work function. However, the threshold voltage can be adjusted by changing the body thickness and gate oxide thickness without need for special gate material. In the asymmetric double gate device, two oxide thicknesses are unequal, the two gates have different flat-band voltage and two different gate biases. In the asymmetric DG MOSFET with a mid-gap gate electrode, the bands in silicon are not flat in the sub-threshold regime [85].

Fig. 1.9 The Schematic of the double gate MOSFET.

Moreover, there are two operating modes for DG MOSFETs [86]:

• Three-terminal mode: The three-terminal mode refers to the situation where the two gates of DG MOSFET are electrically connected and switched, simultaneously.

• Four-terminal driven (or independently driven) mode: When operated in four-terminal driven mode, the two gates are biased differently with only one gate switching. The four-terminal driven mode enables the possibility of dynamic threshold voltage adjustment in circuit design and thus enlarges circuit design space.

Fig. 1.10 shows the different structures and two operating modes of the DG MOSFET. However, the four-terminal driven DG MOSFETs exhibit non-ideal sub-threshold slope. This is because the potential across the silicon film does not move along as a whole with the switching gate if the potential of the non-switching gate is fixed. Moreover, the four-terminal driven DG MOSFET also shows worse short-channel effect than the commonly used three-terminal driven DG MOSFET.

Fig. 1.10 The schematics of DG MOSFET structure. (a), (b) tied gates and (c), (d) separated gates. [86].

Due to high gate-to-substrate coupling, the device produces a near ideal subthreshold slope (60 mV/dec) and flexible threshold voltage control can be offered by the separation of the two gates [87]. This device has less parasitic capacitances as compared to that of the conventional MOSFET, however the important thing is the proper alignment of the front and back gate, as the misalignment contributes to the parasitic capacitances. The thickness of body has to be controlled to reduce the parasitic resistances, which are in the series with the channel and source/drain electrode. However, when the scattering due to impurity or coulomb scattering is absent, then the carrier mobility is significantly high. The carrier mobility degradation which is related to gate field reduces due to the lightly doped/undoped substrate film for the given oxide thickness. However, as both the gates are close to channel, there is the dominant control over the channel electrostatics.

Moreover, double gate MOSFET has an advantage of the architectural feature which is useful for the design of extraordinarily radio frequency analog integrated circuits and adaptive systems, with less difficulty in fabrication processes. Although, it is pointed out that the device has much better potential in this form of application, if the top and bottom gates are driven independently [88], which further increases the operational capability, reduces the parasitic capacitances and layout area and increasing the speed with reduced the power consumption as compared to that of the conventional MOSFET's. Moreover, this is a useful method to tune the response of conventional CMOS analog circuits, especially, for current-mode design [89]. DG-MOSFETs cover the way for capable, tolerant and reduced circuit size with tuneable features.

#### 1.4.1.1. Related Work

Various researchers/scientists have devoted their hard work in developing compact models for DG MOSFET. Balestra et al [90] demonstrated that the double gate MOSFET force the whole silicon body thickness in the strong inversion. The volume inversion effect is quite significant when the gate-source voltage is less than that of the threshold voltage. In addition to this, Taur et al [91] also presented an analytical model based on the charge sheet approximation for symmetric double gate (SDG) MOSFET and analyzed the threshold voltage ( $V_{th}$ ), which is independent of the silicon body thickness ( $t_{si}$ ). However, an exponential

decrease in the saturated value of current with the drain-source voltage ( $V_{ds}$ ) is seen, as compared to that of the common piecewise models where the current is made to be constant in saturation.

Lu et al [92] have purposed the model based on the Poisson equation and the current continuity equation without the charge sheet approximation. Moreover, the authors presented the threshold voltage of ADG MOSFETs that is the function of silicon thickness. Therefore, the sub-threshold current is much more sensitive to the silicon film thickness, as compared to that of the SDG MOSFET. However, the ADG MOSFET with thicker silicon film has a lower threshold voltage and thus higher sub-threshold current.

Ortiz Conde et al [93] developed an accurate drain current model consistent with the drift-diffusion transport and based on the Pierret and Shields formulation which is valid for all the operating conditions. In addition to this, Ortiz Conde et al [94] also developed the analytical solution for the surface potential of un-doped body SDG MOSFET using the principle branch of the Lambert W function. However, for achieving the desired circuit performance of DG structure, Balasubramaniam et al [95] analyzed, the effective channel length, that is larger than the physical gate length and the circuit performance is enhanced by using the thin-body DG MOSFET. However, the effect of random dopant fluctuation and junction capacitances are reduced significantly as the lightly doped or undoped body is used. The variation in the source drain separation for achieving a better drive current can be performed, however trade-off between SCE with series resistance has to be maintained. The result illustrated that the optimal gate-to-Source-drain overlap for maximizing circuit performance is lesser than that needed to maximize the drive current [95]. Antoine et al [96] investigated the non-Colombian scattering, and the reason behind the degradation of mobility below 100 nm gate, ariseing because of the presence of neutral defects in Si or at the interface near the source and drain. The author also illustrated that the defects can be improved by annealing temperature from 1050 °C to 1080 °C. Mahapatra [97] investigated the effect of the gate and channel engineering on the leakage

current, drain induced barrier lowering (DIBL), which would further improve circuit speed and power consumption. The author's results demonstrate that the DG-DI MOSFET has better performance as compared to that of the other counterparts. The fringing induces barrier lower (FIBL) is studied by Charmi [98] which arises when the effective oxide thickness is comparable to the gate length. Moreover, the reduction of FIBL can be performed by using under-lap source/drain region. Evans et al [99] analyzed that the carrier penetration into the oxide is not accounted for in the density gradient method, therefore the first principle calculation can be used to optimize an accuracy of the density gradient method for modeling of the device. Moreover, the position of the impurity in the channel plays a significant role and it degrades the current in the device, therefore Dollufus et al [100] analyzed this effect on the single gate MOSFET as well as the DG MOSFET in addition to the velocity overshoot effect for both the device structures. The authors [100] illustrated that the degradation in the performance of single-gate MOSFET is more pronounced with more significant effect observed for the p-type impurity. For a DG MOSFET, the effect of negative gate overlap and the control of back gate bias is analyzed in [101], which illustrate that if the overlap is negative the device performance is degraded. However, if the back gate bias is high, the threshold voltage is reduced which further increases the circuit speed due to the increase in the ion and if the bias is low, the threshold voltage is increased, which can reduce the power dissipation. Therefore, depending upon the application a trade of can be maintained in high on-current and low power dissipation. Based on the charge coupling between the source and the drain end and the front and the back surface potential, Ortiz-Conde et al [102] developed the drain current and the trans-conductance model for the un-doped asymmetric double gate MOSFET. The variation of trans-conductance and the sub-thresholdslope is analyzed based on the variation of the back gate bias. Taur [103] has analyzed a un-doped body asymmetric DG MOSFET symmetry point shifts from the center to some point in the silicon body and is minimum at that point. Moreover, the threshold voltage dependencies on the dimensions of asymmetric DG MOSFET have been studied for the long- and short-channel and then

compared with the threshold variation with a symmetric DG MOSFET in [104]. Cakici and Roy [105] performed a case study on Schmitt trigger to analyze the effect of using connected gates or independent gates DG MOSFET and the results illustrates that high noise immunity at low dynamic power dissipation can be achieved by the independent operating gates. Although, an increase in the delay, leakage power and process variation are the significant undesirable by-products for the device performance. Moreover, the dynamic threshold voltage control is feasible with the use of independent gates DG technology. In addition to this, Ruchika et al [106] also explored the design possibilities of the double gate MOSFET for achieving low power application. Roy et al [107] developed a model for a low density of state material in Double gate MOSFET by using both Fermi-Dirac statistics and field dependent diffusivity. A compact model has been developed in [108] for a junctionless double gate MOSFET. Mattausch et al [109] pointed out that to the future requirements of the technology, the surface potential model based on drift- diffusion approximation is essential.

However, Wie et al [110] have showed that, the minimum channel length of the DG SOI MOSFET can be reduced to 30% as compared to that of the conventional MOSFET, which would further increase the cutoff frequency and making it a better candidate for low voltage and low power applications. Kumar et al [111] explored the influence of channel and gate engineering on the analog/RF performance of DG MOSFET and analyzed that the gate and channel engineering, which increases the gain by 45%, 35% respectively compared to that of the single gate MOSFET. However, the channel engineered devices shows the reduction of the cutoff frequency. The advantages of triple material DG MOSFET over the dual material and single material DG MOSFET are discussed in [112]. The authors have analyzed the performance enhancement in terms of the intrinsic gain of 20.41% and 38.53% for dual material DG MOSFET and the triple material DG MOSFET respectively, unity gain frequency of 14.23% and 26.4% for dual material DG MOSFET and the triple material DG MOSFET respectively, and maximum oscillation frequency of 13.9%,23.85% for dual material DG MOSFET

and the triple material DG MOSFET respectively, which shows the device structure can provide enhanced performance for high frequency RF applications. Kumar et al [113] analyzed the SCE reduction and RF performance enhancement of the single halo dual material DG MOSFET compared to the single halo counterpart. The realization of high performance analog and RF circuits is possible by the use of high dielectric gate stack DG MOSFET [114].

#### **1.4.2. Surrounding Gate MOSFET**

The structure of the surrounding gate MOSFET is similar to the double gate MOSFET only the difference lie in that the channel is surrounded by the gate from all sides which reduces the leakage current in the device and further the performance of the device increases. Moreover, it also provides, approximately 30% reduction in the length of the device is achieved than that of the double gate MOSFET with a given silicon body thickness ( $t_{si}$ ) and oxide thickness ( $t_{ox}$ ) [115] which further increases the packing density. The flow of current is vertical along the cylindrical Si/SiO2 interface and the gate length of the transistor is defined by the height of the gate material. The tight capacitive coupling in all direction reduces the SCE. The General Surrounding gate MOSFET structure is shown in Fig. 1.11. However, the vertical orientation of the device on a single chip reduces the chip area and is also a much researched area.

Fig. 1.11 The Schematic of surrounding gate MOSFET.

#### 1.4.2.1. Related Work

The surrounding gate MOSFET is very effectively scaled down to the nanometer regime for low power and high speed applications [116]. Rustagi et al [117] have analyzed the surrounding gate MOSFET, is very effective for the high speed and low power circuit application. Iniguez et al [118] developed a DC model for surrounding gate MOSFET based on the charge controlled model, and the continuity of the channel current, which is preserved throughout all the operating regions therefore the model is effective for circuit simulations. Jimenez et al [119] also developed a model for the lightly doped surrounding gate MOSFET without any fitting parameter. Bian et al [120] have derived a model based on both the drift and diffusion current components based on the analytical potential approach, including the potentials at the oxide silicon interface and silicon center. Yu [121] has developed a model for the depletion mode surrounding gate nano-wire FET with capturing the conduction mechanism from sub-threshold to saturation region. The model for surrounding gate MOSFET is developed by taking into account the polysilicon depletion effect [122]. However, Roy et al [123] have developed a model for the surrounding gate MOSFET based on the Gaussian law instead of the Poisson equation. A potential based model for the dual material surrounding gate MOSFET before the onset of strong inversion, is analyzed in [125] based on the parabolic approximation to understand the short channel effects due to gate engineering. A new technique of general series solution method [126] is also developed for solving the cylindrical Poisson equation which is very effective in observing the various short channel effects that is threshold voltage, drain induced barrier lowering (DIBL) etc. The high level of doping and ultra thin oxide is a major requirement to reduce these short channel effects. Pandian and Balamurugun [127] have proposed a threshold voltage based model for the short channel surrounding gate nano-wire transistors with two forms of geometry that is junction based surrounding gate MOSFET and rectangular surrounding gate MOSFET. The major difference between these two geometries is the rectangular gate device is bound to get affected by corner effects much more in comparison

with the cylindrical gate device. The model for surrounding gate MOSFET including different fringing gate capacitance is developed [128], which is valid for the short channel devices with  $L_g$ = 15 nm and long channel devices with  $L_g$ = 50 nm. However, based on the charge control model, the authors in [129] developed an analytical expression of the total capacitance of un-doped body surrounding gate MOSFET as the function of voltages. Kranti et al [130] have developed a model for the short channel surrounding gate MOSFET accounting for the effect of field dependent mobility, velocity saturation, and source-drain resistance effect.

Ruiz et al [131] have developed a model for the total gate capacitance of surrounding gate transistors and based on the result the authors have compared the capacitance behaviour of the DG MOSFET and surrounding gate MOSFET and illustrated that the capacitance is less in surrounding gate MOSFET as compared to DG MOSFET due to the greater confinement by the gate.

A comparative study of the single material gate and gate material engineering surrounding gate MOSFET is performed in [132]. In addition to this, the effect of interface trap charges on the RF and linear distortion analysis is also presented. The results indicate that the gate material engineered surrounding gate MOSFET provides a better immunity against the interface charges and can maintain efficient device linearization, which makes the device useful for the radio frequency integrated circuit application. Sarkar et al [133] have analyzed the performance potential of the SRG MOSFET in the RF/Analog circuit's applications and discusses the performance of the device without including the quantum mechanical effects. Moreover, for the analog performance, high value of the trans-conductance generation factor ( $g_m/I_d$ ) is needed.

With the development of the surrounding-gate MOSFET in the nano-meter regime, the high frequency capability of the transistors has reached to the GHz regime which is well suited for the radio frequency circuit applications [134, 135]. Hagh and Bindal [136] have discussed due to the full gate control over the channel, the vertical surrounding gate MOSFET can achieve low off-state current,

which makes the surrounding gate MOSFET as a promising device for very large scale integration technology. Moreover, the gate material engineered transistor shows better immunity against the influence of interface trap charges and exhibits significant enhancement to maintain the device linearization, as compared to a single material gate junction-less surrounding-gate MOSFET, so that it can be used as a high-efficiency linear radio-frequency integrated-circuit design and wireless applications [137]. Gautam et al [138] have analyzed the gate all around MOSFET with the vacuum as the dielectric, which is a better candidate for the high speed RF applications. Although, the trans-conductance and on-state drain current is reduced, but it can be enhanced by using the gate all around MOSFET has the highest cutoff frequency. However, the dual material gate junction-less nano-wire transistor [139] has an advantage of high on-state drain current high unity gain frequency and high maximum oscillation frequency, further which prove to be an efficient structure of the RFIC applications.

### **1.5. Problem Statement**

The demand of the communication industry is increasing for the developments of the devices to handle high data rate and further the high frequencies. Moreover, the improvement in the communication market is also critically dependent on the dimension reduction of the devices. However, the conventional scaling, a tool for the MOS technology advancement into the nano-scale regime, has been hindered by many factors like the short effects (SCE), channel carrier mobility degradation, the hardiness of the circuit with respect to the process variations, etc., that is a vital concern for the circuit designers, which further results in the significant control of the drain on the channel potential. Therefore, the potential need is to minimize the effects of the drain on the channel potential that inspire numerous researchers/scientists for other non-conventional structures like SOI, pie-gate, and omega-gate MOSFET. However, recently, a lot of importance is being given on the double-gate (DG) MOSFET and surrounding gate MOSFET, as these devices scale down to the shortest channel length possible for a chosen oxide thickness,  $30 \mid P \mid a \mid e$

which further reduces the short channel effects. Therefore, this study focuses on the Double-gate MOSFET and surrounding-gate MOSFET modelling and device characterization.

#### **1.6.** Dissertation Organization

This chapter describes the field of study and reviewed previous relevant literature. However, the key research issues and challenges are also identified. The remainder of the chapters is discussed as follows.

**Chapter 2** discusses the symmetric DG MOSFET with its design philosophy and working operation. Further, the performance of the symmetric DG MOSFET based on the potential distribution, sheet charge, drain current, terminal charges and trans-capacitance are also analyzed based on the purposed simulation model.

**Chapter 3** deals with the analysis of the surrounding gate MOSFET using the surface potential distribution, drain current, trans-conductance, output-resistance, on-state resistance, terminal charges, and trans-capacitance of the device. Moreover, the discussion on the effects of Gaussian doping on MOSFET performances such as the potential as well as the characteristics of the MOSFET is also included.

**Chapter 4** discusses the basic performance parametric analysis of the double gate MOSFET and surrounding-gate MOSFET as a amplifier and as a switch through the use of the equivalent circuit approach which is useful for the analysis of the dynamic performance of certain MOSFET.

Finally, in **Chapter 5**, we summarize our work and suggest various directions in which this research can be extended in the future.

## CHAPTER 2 PERFORMANCE ANALYSIS OF DOUBLE-GATE MOSFET

## **2.1. Introduction**

Balestra et al. [90] purposed the first double gate MOSFET with significant volume inversion effect. Currently, the double-gate MOSFET is a subject of intense VLSI research and seen as a replacement for conventional bulk MOSFET beyond the 45 nm technology [140] as it can be scaled to the shortest possible channel length for a given oxide thickness and more electro-statically robust than the earlier reported MOSFETs due to the dual gate shielding and the reduced short-channel effects [77]. Fossum et al [141] have analyzed the higher processing speed of DG MOSFET as compared to that of the SG MOSFET. Fig. 2.1 shows the schematic of a Double Gate MOSFET and the Fig. 2.2 Illustrates the two major DG MOSFET structures: a) asymmetric type with both gates of identical work-functions ( $\phi$ ) where both the surfaces channels turn on at the same gate voltage [142] and b) an asymmetric type with either different work function of the gates ( $\phi$ ,  $\phi'$ ) or different gate oxide thicknesses and only one channel turns on at the threshold voltage [84].

Fig. 2.1. Schematic of the DG MOSFET.

Fig. 2.2 (a) Symmetric Double Gate MOSFET, (b) asymmetric Double Gate MOSFET.

Taur et al [143] derived the analytical model based on the charge sheet approximation which is applicable to all operating regions such as cutoff, linear and saturation. Yu et al [144] purposed an algorithm and the PSP model for the approximation of the surface potential of both the DG MOSFET and SG MOSFET. The model can cover all the operating regions without any use of fitting parameters or charge sheet approximation. The state-of-the-art of the compact models for un-doped DG MOSFET using the 1-D Poisson equation with the introduction of the SCE is discussed in detail in [145]. Riza and Roy [105], have studied the effect of using connected gates or independent gates DG MOSFET, and illustrated that the significantly higher noise immunity at low dynamic power dissipation can be achieved by the independently operating gates as it increases the gate-to-gate coupling. Singh and Jiang [146] showed that with the help of asymmetric DG MOSFET high performance and low power circuits are feasible in the nanometre regime. Therefore, this structure can be used in phase-locked loop where the requirement is a high speed, low voltage and low power operation [147]. Further, the other application of the symmetric DG MOSFET is as a fast switching device [148]. Recently, Srivastava et al. [149, 150] has analyzed the double gate MOSFET and cylindrical surrounding double gate MOSFET for the application as a double pole four throw switch.

#### 2.2. Symmetric Double Gate MOSFET

The planer DG MOSFET is an extension of the single gate MOSFET that consists of two gates designated as front-gate and back-gate, within which the ultra thin silicon layer is sandwiched [83]. The additional gate significantly increases the electrostatic gate control over the channel and these gates are effective in shielding the drain electric field-lines from reaching the source to reduce the potential barrier as well as reducing the SCE. Due to un-doped/lightly doped body, the problem of random dopant fluctuation is also absent. Moreover, both the gates contribute to inversion carriers, which have high drive capability and two channels for the current flow are formed, when these two gates simultaneously control the charge. In addition to this, as the silicon film is very thin there exists a better coupling between front- and back-gate which affect the terminal characteristics of the MOSFET.

Fig. 2.3 The band model of the symmetric DG MOSFET a)  $V_{gs} = 0$  V b)  $V_{gs} = V_{th}$  [143].

For the symmetric double-gate device structure, at the zero gate voltage the silicon bands are flat for the mid-gap gate work function as shown in Fig. 2.3 (a). However, at  $V_g = V_{\text{th}}$ , the conduction band edge of the silicon body near the surface is bent as shown in Fig. 2.3(b) and approaches the conduction band edge

of the n+ source/drain. However, the conduction bands in both surfaces (under the front and back gates) are bent by the similar amount as the work functions of two gates are identical. At ON-state, two conductive channels are formed in the symmetric double-gate device, unless the silicon body thickness is not very thin [92].

## 2.3. Analysis

In this section, we have analyzed the 1-D Poisson's equation in the Cartesian coordinate system with gradual channel approximation which is given as:

$$\frac{d^2\psi}{dx^2} = \frac{qn_i}{\epsilon_{si}} e^{\frac{q(\psi-V)}{KT}}$$

(2.1)

where, q,  $\epsilon_{si}$ ,  $n_i$ , K, and T are the electron charge, dielectric permittivity of silicon, intrinsic carrier density, the Boltzmann constant, and operating temperature, respectively. V represents the quasi-Fermi potential V=0 at source side and  $V=V_{ds}$ at drain side. We have considered the n<sup>+</sup> DG MOSFET, therefore the hole density is negligible and the silicon film is un-doped or lightly doped that is:

$$n_b << n_i * e^{\frac{q\psi}{KT}} \tag{2.2}$$

where,  $n_b$  is the doping concentration. However, integrating (1) twice, we can get the potential distribution equation as a function of 'x' which is position in the silicon body thickness.

In the symmetric DG MOSFET, the electric field is zero at x = 0 that is the center of the silicon body thickness. The surface potential ( $\Psi_s$ ) for DG MOSFET is as: