## **Comparative Study of Topologies in 3D NoC**

Project report submitted in partial fulfillment of the requirement for the degree of

Master of Technology in Computer Science and Engineering

> By Suchi Johari (132208)

Under the Supervision of

### Dr. Vivek Kumar Sehgal

Department of Computer Science and Engineering Jaypee University of Information and Technology Waknaghat, Solan – 173234, Himachal Pradesh, India

## Certificate

This is to certify that project report entitled **Comparative Study of Topologies in 3D NoC**, submitted by **Suchi Johari** in partial fulfillment for the award of degree of Master of Technology in Computer Science and Engineering to Jaypee University of Information Technology, Waknaghat, Solan has been carried out under my supervision.

This work has not been submitted partially or fully to any other University or Institute for the award of this or any other degree or diploma.

DATE:

SUPERVISOR: Dr.Vivek Kumar Sehgal Associate Professor Department of CSE and IT

## Acknowledgements

I Suchi Johari would like to thank **Prof. Dr. RMK Sinha (Dean CSE and IT)** and **Prof. Dr. S.P Ghrera (Head, Dept. of CSE)** for all the support and guidance they have provided to me during my M.Tech programme. I am thankful for his continuous motivation and encouragement provided to me at every point in time.

I would like to thank **Dr. Vivek Kumar Sehgal (Associate professor, Department of CSE and IT)** for offering me the opportunity to do my post graduation project under his supervision at Jaypee University of Information Technology. In the meetings and discussions, he always gave me right advice and he directed my research in the right direction.

I would also like to thank **Dr. Pardeep Kumar** (Associate M.Tech Research Coordinator) for his valuable guidance and motivation. I am thankful to my seniors and friends for their support and help provided during the completion of this thesis. I would sincerely like to thank all the librarian for their support and help by providing me the study material.

Finally I would like to express my profound thanks to my parents for teaching me how to soar. I would not have made it this so far without their unbounded love, guidance, support and most importantly their prayers.

DATE:

SUCHI JOHARI(132208) M.Tech C.S.E. 2<sup>nd</sup>yr ii

## **Declaration**

I hereby declare that the thesis entitled "Comparative Study of Topologies in 3D NoC" submitted by me for the award of degree of Master of Technology in Computer Science and Engineering, Jaypee University of Information Technology, Waknaghat is original and it has not submitted previously to this or any other university for any degree or diploma. Signature of

Student : Name of Student : Date :

## Abstract

Networks on Chip is a communication subsystem on an integrated circuit (commonly known as "chip"). As the number of cores and IP blocks integrated on a single chip are increasing day by day, there is a need to design such a topology which proves to be best for communication, satisfying all the quality of service(QoS) parameters such as latency, throughput, link-utilization, loss probability and energy consumption at constant bandwidth required. Till now the topologies are optimized on the basis of cost and design space. Now the target is to minimize the global communication traffic, along with the cost and space. Throughput, latency and energy consumption are the basic parameters to consider communication between modules. Shorter the communication path, lesser is the latency. Power consumption also depends upon the length of wires and data activity. For this reason, 3D Networks-on-Chip is gaining more popularity as compared to 2D Networks-on-Chip. In order to reduce space and cost of the chip, Networkson-Chip tries to reduce the number of connections. But reduction in number of connections lead to lack in functionality during traffic and noise, as lesser the number of communication path between any two nodes more chances of bottleneck, leading to the lack of performance. Keeping all these issues in mind, the main concern is to reduce communication delay keeping size and cost constant. The aim of this research work is to do comparative studies of all the topologies being developed for 3D networks-on-chip, and designing a full fledged new topology which proves to be better than the existing ones in all the senses. This report summarizes the concepts of the existing topologies for the on chip networks and gives overview of how different topologies are beneficial over the other.

# Contents

1

| Cert | tificate |                                | i   |

|------|----------|--------------------------------|-----|

| Ack  | nowled   | gements                        | ii  |

| Decl | laration |                                | iii |

| Abs  | tract    |                                | iv  |

| Intr | oductio  | n                              | 1   |

| 1.1  | Why 3    | D NoCs?                        | 2   |

| 1.2  | Flit siz | e or Phit Size                 | 4   |

| 1.3  | Routin   | g                              | 5   |

|      | 1.3.1    | Distributed Routing            | 5   |

|      | 1.3.2    | Source Routing                 | 5   |

|      | 1.3.3    | Hybrid Routing                 | 6   |

|      | 1.3.4    | Centralized Routing            | 6   |

| 1.4  | Impler   | nentation of Routing Algorithm | 6   |

v

|                    | 1.4.1                                                        | Deterministic routing algorithms                                                                                                                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | 1.4.2                                                        | Oblivious routing algorithms                                                                                                                                                              | 7                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | 1.4.3                                                        | Adaptive routing algorithms                                                                                                                                                               | 7                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.5                | Switch                                                       | ing                                                                                                                                                                                       | 7                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | 1.5.1                                                        | Circuit Switching                                                                                                                                                                         | 7                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | 1.5.2                                                        | Store-and-forward (SF) switching or Packet Switching                                                                                                                                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | 1.5.3                                                        | Virtual cut-through (VCT) switching                                                                                                                                                       | 8                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | 1.5.4                                                        | Wormhole (WH) switching                                                                                                                                                                   | 9                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.6                | Router                                                       | Architectures                                                                                                                                                                             | 12                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    |                                                              |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Lite               | rature I                                                     | Review                                                                                                                                                                                    | 14                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>Lite</b><br>2.1 |                                                              | <b>Review</b><br>ch Papers                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |                                                              |                                                                                                                                                                                           | 14                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | Resear                                                       | ch Papers                                                                                                                                                                                 | 14                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | Resear<br>2.1.1                                              | ch Papers                                                                                                                                                                                 | 14<br>14<br>15                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    | Resear<br>2.1.1<br>2.1.2                                     | ch Papers          Key Research Problems in NoC Design: A Holistic Perspective          3D Network-on-Chip Architectures Using Homogeneous Meshes and       Heterogeneous Floorplans [43] | 14<br>14<br>15                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    | Resear<br>2.1.1<br>2.1.2<br>2.1.3                            | ch Papers                                                                                                                                                                                 | 14<br>14<br>15<br>17                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | Resear<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4                   | ch Papers                                                                                                                                                                                 | 14<br>14<br>15<br>17<br>17                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1                | Resear<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6 | ch Papers                                                                                                                                                                                 | 14<br>14<br>15<br>17<br>17<br>18                                                                                                                                                                                                                                                                                                                                                                                    |

|                    |                                                              | 1.4.2<br>1.4.3<br>1.5 Switch<br>1.5.1<br>1.5.2<br>1.5.3<br>1.5.4                                                                                                                          | 1.4.2       Oblivious routing algorithms         1.4.3       Adaptive routing algorithms         1.4.3       Adaptive routing algorithms         1.5       Switching         1.5       Switching         1.5.1       Circuit Switching         1.5.2       Store-and-forward (SF) switching or Packet Switching         1.5.3       Virtual cut-through (VCT) switching         1.5.4       Wormhole (WH) switching |

| 4 | Proj | posed A  | pproach                                           | 23 |

|---|------|----------|---------------------------------------------------|----|

|   | 4.1  | Cluster  | r Formation                                       | 24 |

|   | 4.2  | Structu  | are of Router and Core for implementation of CBCT | 26 |

|   | 4.3  | Master   | based Routing Algorithm                           | 30 |

|   | 4.4  | CBCT     | : Communication based Cluster Topology            | 30 |

|   | 4.5  | 3D CB    | CT topologies for NoC                             | 36 |

|   | 4.6  | Quality  | y of Services                                     | 40 |

| 5 | Sim  | ulator T | ìool                                              | 45 |

|   | 5.1  | OMNE     | ET++ Simulator                                    | 45 |

|   | 5.2  | Orion    | 2.0 Simulator                                     | 46 |

| 6 | Desi | ign      |                                                   | 48 |

| 7 | Exp  | eriment  | al Results                                        | 54 |

|   | 7.1  | Experi   | mental results of 3D NoC CBCT topology            | 64 |

|   |      | 7.1.1    | Results of 3D Mesh topology                       | 64 |

|   |      | 7.1.2    | Results of 3D Hybrid topology                     | 64 |

|   |      | 7.1.3    | Results of 3D Layered topology                    | 67 |

|   |      | 7.1.4    | Comparison of Results                             | 67 |

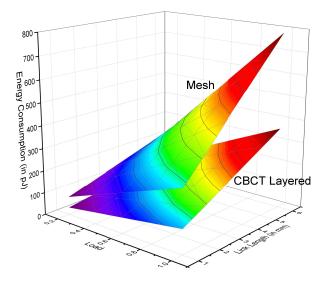

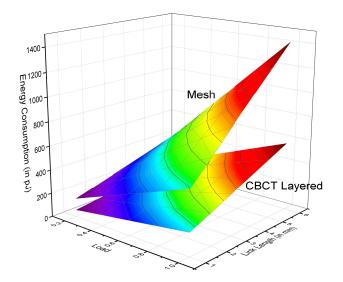

|   |      | 7.1.5    | Results for energy consumption                    | 74 |

| 8 | Con  | clusion  |                                                   | 80 |

| 9 | Future Work          | 81 |

|---|----------------------|----|

|   | Bibliography         | 82 |

|   | List of Publications | 86 |

viii

# **List of Figures**

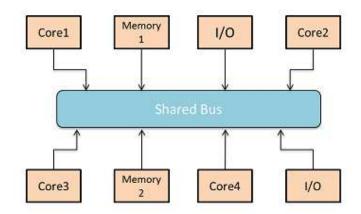

| 1.1 | Shared Bus Architecture                                                    | 2  |

|-----|----------------------------------------------------------------------------|----|

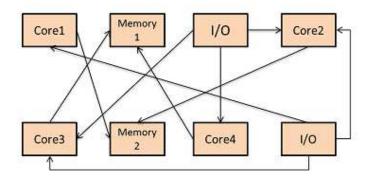

| 1.2 | Point to Point Architecture                                                | 3  |

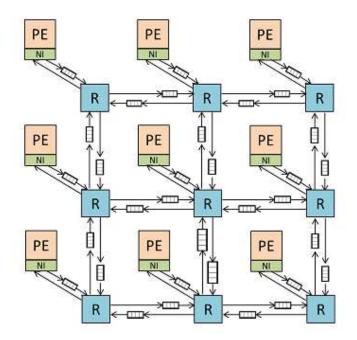

| 1.3 | Networks on Chip Architecture                                              | 3  |

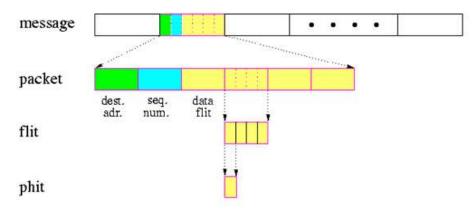

| 1.4 | Phit and Flit                                                              | 5  |

| 1.5 | Circuit Switching                                                          | 8  |

| 1.6 | Store-and-forward (SF) switching or Packet Switching                       | 9  |

| 1.7 | Virtual cut-through switching                                              | 10 |

| 1.8 | Wormhole switching                                                         | 11 |

| 1.9 | Router Architecture                                                        | 13 |

| 2.1 | Floorplans showing the combined use of homogeneous floorplan and heteroge- |    |

|     | neous floorplans.                                                          | 16 |

| 2.2 | Various NoC Topologies                                                     | 18 |

| 2.3 | ACP and CRG                                                                | 19 |

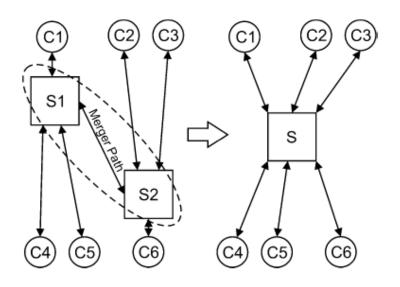

| 2.4 | Example of switch merger.                                                  | 20 |

| 2.5 | Example of switch partitioning process.                                    | 20 |

| 2.6  | Topology generation Algorithm.                                                      | 21 |

|------|-------------------------------------------------------------------------------------|----|

| 4.1  | Communication between Cores                                                         | 26 |

| 4.2  | Intra-cluster and inter-cluster communication in CBCT                               | 27 |

| 4.3  | Topology based cluster graph                                                        | 27 |

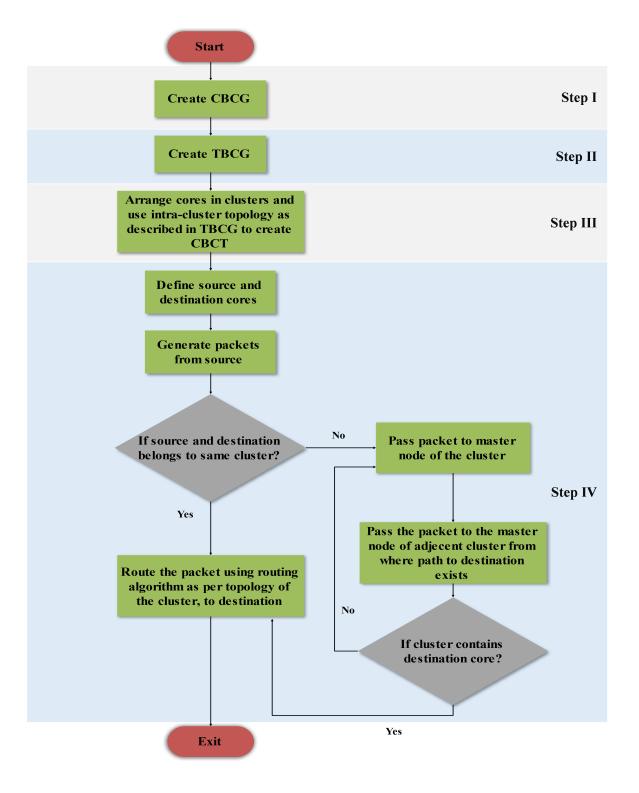

| 4.4  | Flowchart for generating CBCT topology                                              | 28 |

| 4.5  | Structure of 2D router used for CBCT                                                | 29 |

| 4.6  | Structure of 2D core used for CBCT                                                  | 29 |

| 4.7  | 5X5 2D Mesh Topology                                                                | 32 |

| 4.8  | Cluster of most communicating cores                                                 | 33 |

| 4.9  | Communication based Cluster topology                                                | 34 |

| 4.10 | Flowchart for creating CBCT topology and routing packets from source to destination | 35 |

| 4.11 | 5X5 2D Mesh Topology                                                                | 37 |

| 4.12 | Heterogeneous and hybrid Clustered topology                                         | 38 |

| 4.13 | Clustered topology geometrically equivalent to mesh topology                        | 39 |

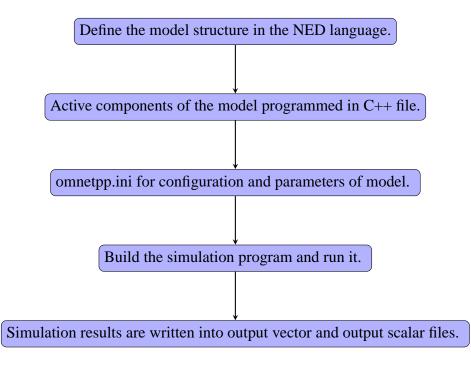

| 5.1  | Flow chart representation of execution of steps in OMNET++                          | 46 |

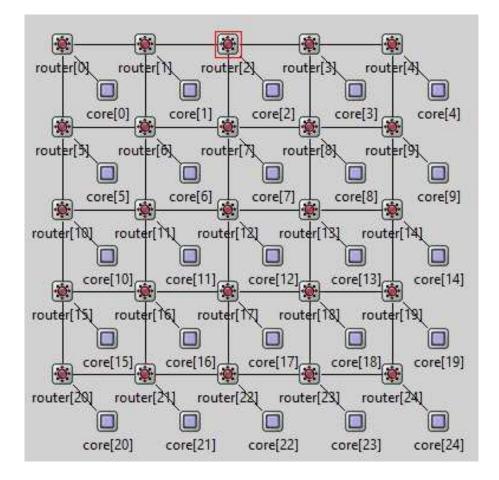

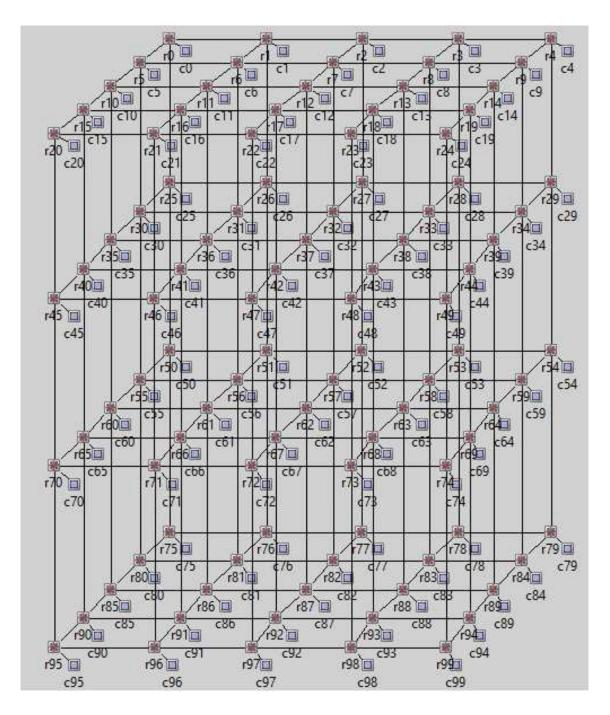

| 6.1  | Design of 5X5 Mesh Topology                                                         | 49 |

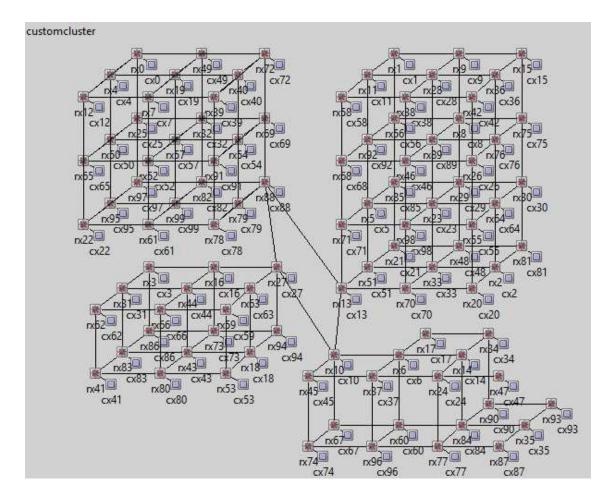

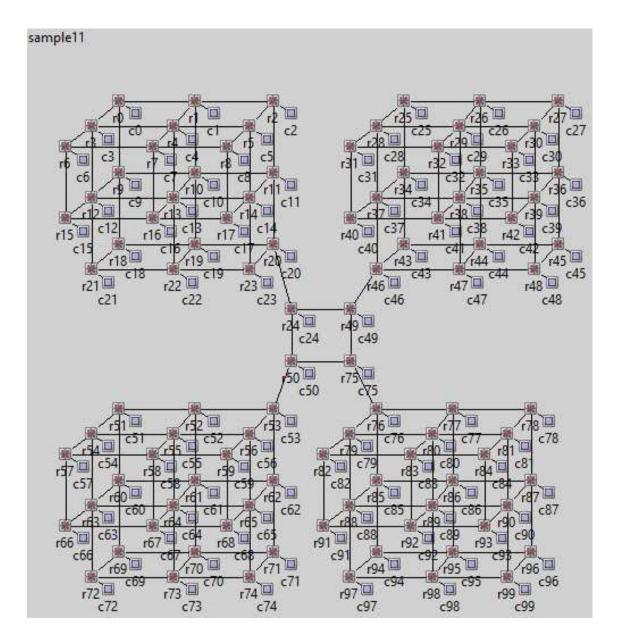

| 6.2  | Design of Cluster based Hybrid Topology                                             | 50 |

| 6.3  | 5X5X4 (100 processing elements) 3D Mesh                                             | 51 |

| 6.4  | Hybrid CBCT topology                                                                | 52 |

#### LIST OF FIGURES

| 6.5  | Layered CBCT topology                  | 53 |

|------|----------------------------------------|----|

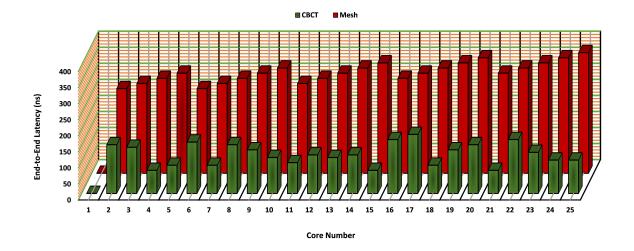

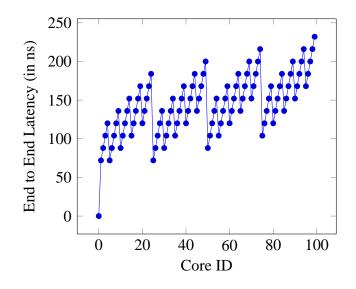

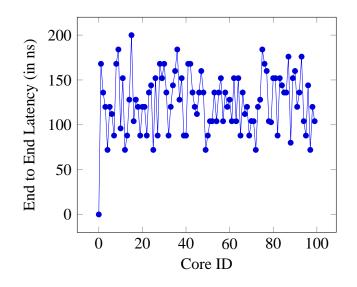

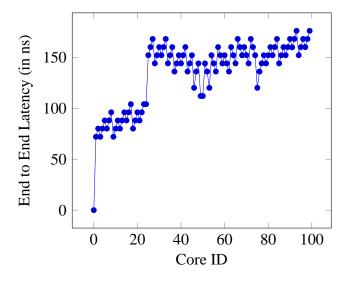

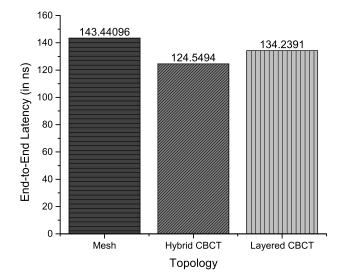

| 7.1  | End-to-End Latency                     | 57 |

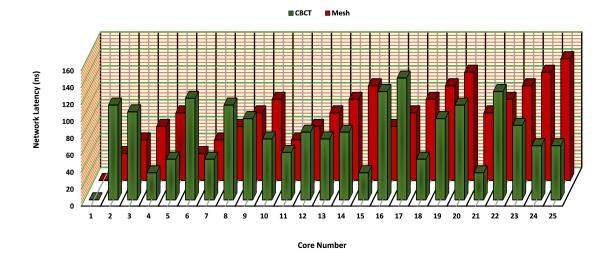

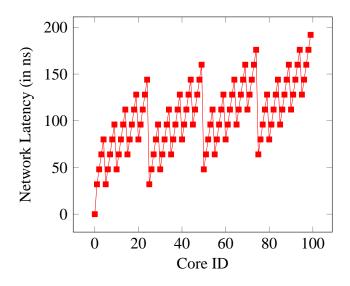

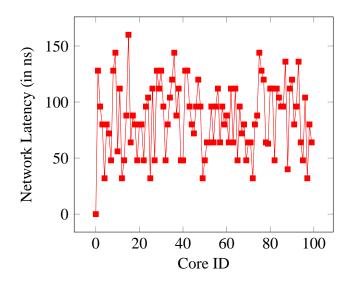

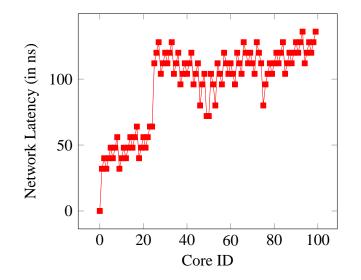

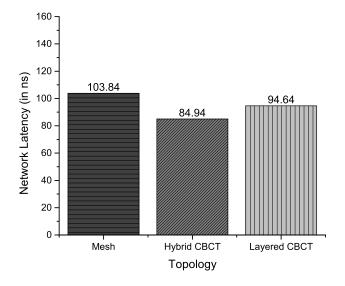

| 7.2  | Network Latency                        | 58 |

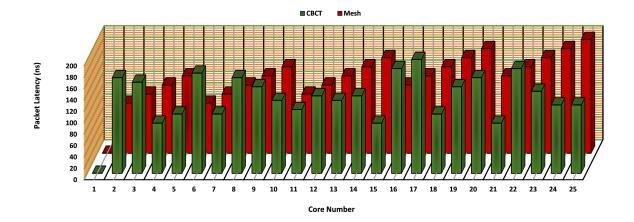

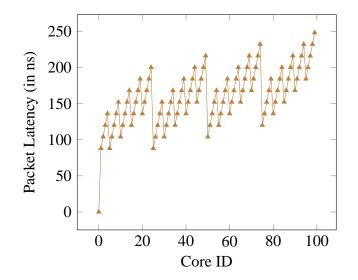

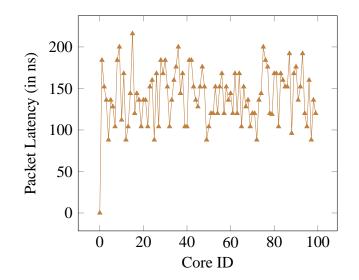

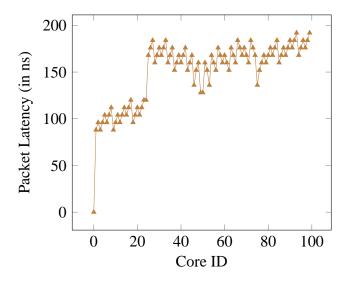

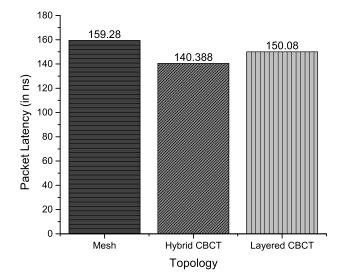

| 7.3  | Packet Latency                         | 58 |

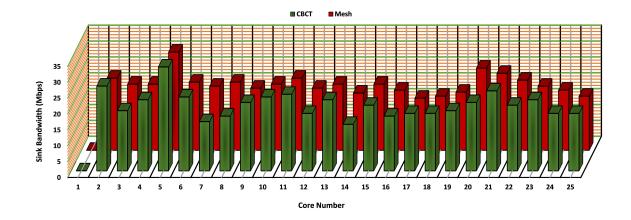

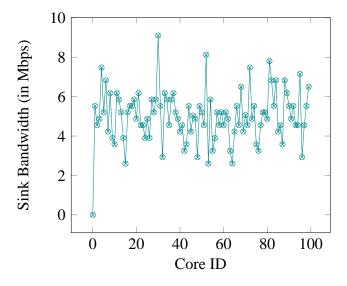

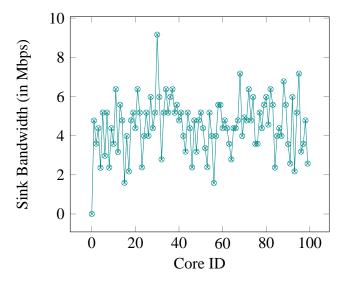

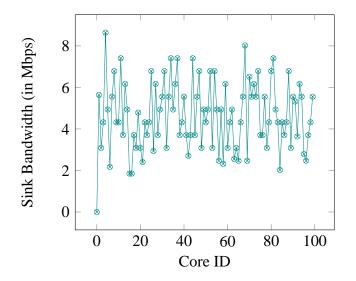

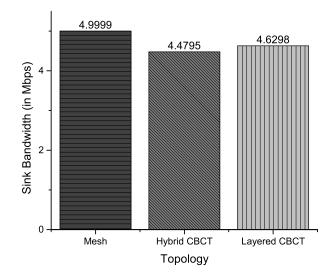

| 7.4  | Sink Bandwidth                         | 59 |

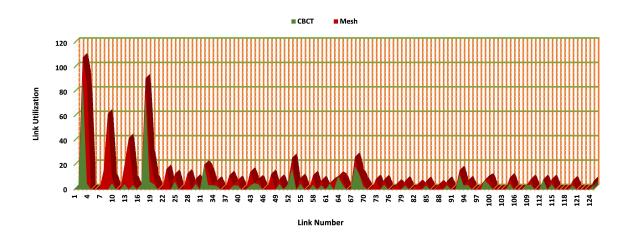

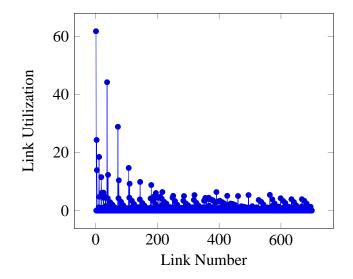

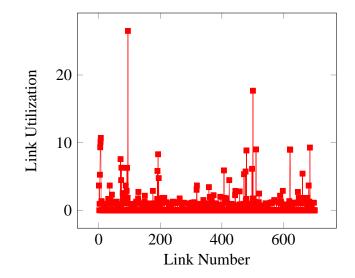

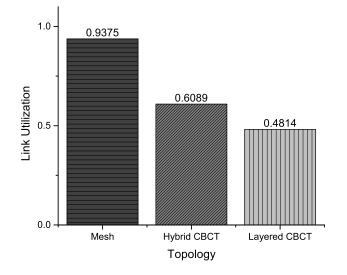

| 7.5  | Link Utilization                       | 59 |

| 7.6  | Energy consumption on core $c_4$       | 61 |

| 7.7  | Energy consumption on core $c_9$       | 61 |

| 7.8  | Energy consumption on core $c_{14}$    | 62 |

| 7.9  | Energy consumption on core $c_{17}$    | 62 |

| 7.10 | Energy consumption on core $c_{19}$    | 63 |

| 7.11 | Energy consumption on core $c_{24}$    | 63 |

| 7.12 | End to End Latency in 3D Mesh Topology | 64 |

| 7.13 | Network Latency in 3D Mesh Topology    | 65 |

| 7.14 | Packet Latency in 3D Mesh Topology     | 65 |

| 7.15 | Sink Bandwidth in 3D Mesh Topology     | 66 |

| 7.16 | Link Utilization in 3D Mesh Topology   | 66 |

| 7.17 | End to End Latency in 3D hybrid CBCT   | 67 |

| 7.18 | Network Latency in 3D hybrid CBCT      | 68 |

| 7.19 | Packet Latency in 3D hybrid CBCT       | 68 |

xi

| 7.20 | Sink Bandwidth in 3D hybrid CBCT                                                                                                                  | 69 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

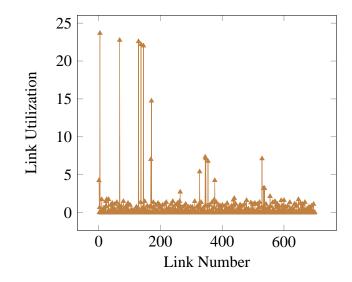

| 7.21 | Link Utilization in 3D hybrid CBCT                                                                                                                | 69 |

| 7.22 | End to End Latency in 3D layered CBCT                                                                                                             | 70 |

| 7.23 | Network Latency in 3D 3D layered CBCT                                                                                                             | 70 |

| 7.24 | Packet Latency in 3D layered CBCT                                                                                                                 | 71 |

| 7.25 | Sink Bandwidth in 3D layered CBCT                                                                                                                 | 71 |

| 7.26 | Link Utilization in 3D layered CBCT                                                                                                               | 72 |

| 7.27 | Comparison of End-to-End Latency                                                                                                                  | 72 |

| 7.28 | Comparison of Network Latency                                                                                                                     | 73 |

| 7.29 | Comparison of Packet Latency                                                                                                                      | 73 |

| 7.30 | Comparison of Sink Bandwidth                                                                                                                      | 74 |

| 7.31 | Comparison of Link Utilization                                                                                                                    | 75 |

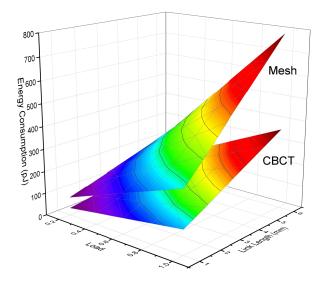

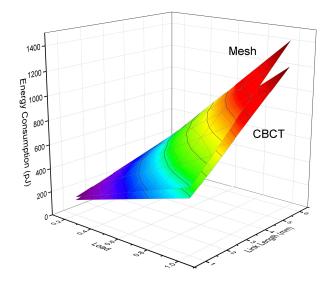

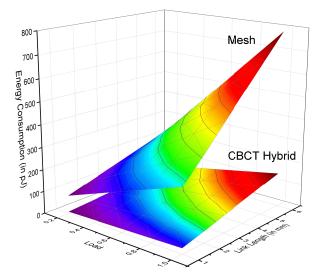

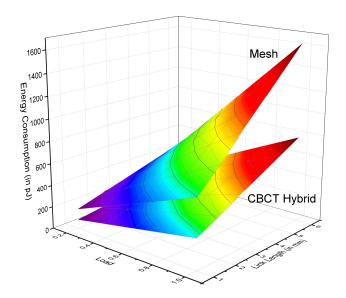

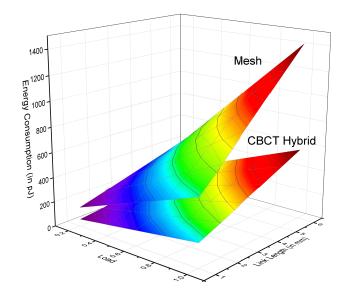

| 7.32 | Comparison of energy consumption (in pJ) in $c_4$ core (a) 3D Mesh (b) 3D<br>Cluster based Hybrid Topology(clustering of layers of Mesh Topology) | 75 |

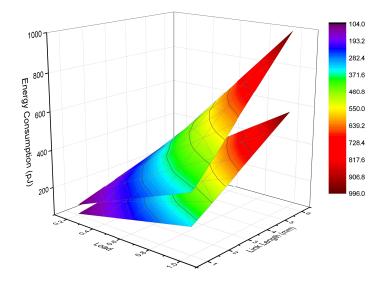

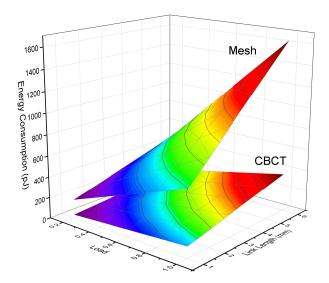

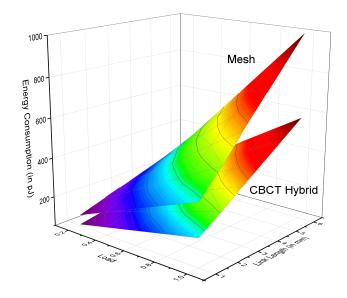

| 7.33 | Comparison of energy consumption (in pJ) in $c_{57}$ core (a) 3D Mesh (b) 3D Cluster based Hybrid Topology(clustering of layers of Mesh Topology) | 76 |

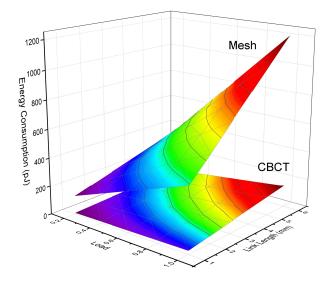

| 7.34 | Comparison of energy consumption (in pJ) in $c_{88}$ core (a) 3D Mesh (b) 3D Cluster based Hybrid Topology(clustering of layers of Mesh Topology) | 76 |

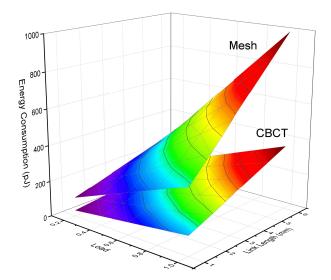

| 7.35 | Comparison of energy consumption (in pJ) in $c_{95}$ core (a) 3D Mesh (b) 3D Cluster based Hybrid Topology(clustering of layers of Mesh Topology) | 77 |

| 7.36 | Comparison of energy consumption (in pJ) in $c_4$ core (a) 3D Mesh (b) 3D Cluster based Layered Topology(clustering of layers of Mesh Topology)   | 77 |

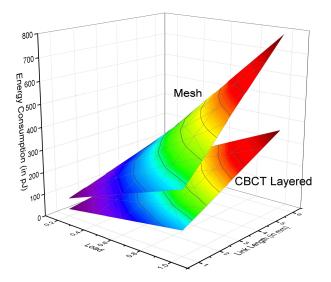

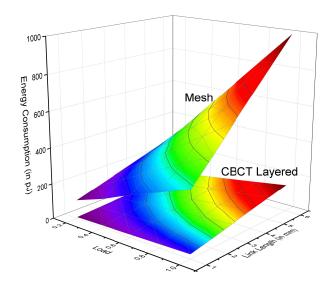

- 7.37 Comparison of energy consumption (in pJ) in c<sub>9</sub> core (a) 3D Mesh (b) 3D

Cluster based Layered Topology(clustering of layers of Mesh Topology) . . . . 78

- 7.38 Comparison of energy consumption (in pJ) in c<sub>12</sub> core (a) 3D Mesh (b) 3D

Cluster based Layered Topology(clustering of layers of Mesh Topology) . . . . 78

- 7.39 Comparison of energy consumption (in pJ) in c<sub>19</sub> core (a) 3D Mesh (b) 3D

Cluster based Layered Topology(clustering of layers of Mesh Topology) . . . . 79

## **List of Tables**

| 7.1 | Parameters considered for simulation of mesh topology and CBCT                         | 55 |

|-----|----------------------------------------------------------------------------------------|----|

| 7.2 | Parameters considered for calculation of Energy Consumption in mesh topology and CBCT. | 55 |

| 7.3 | Simulation details for mesh topology and CBCT                                          | 56 |

| 7.4 | Energy consumption of Link (in pJ)                                                     | 60 |

| 7.5 | Energy consumption of Router (in pJ).                                                  | 60 |

## Chapter 1

## Introduction

System-on-chip has performance issues due to interconnection networks. Basically while concentrating over the issues such as scalability, high bandwidth and low latency system on chip tries to become as smaller as possible by shrinking the size of the chip. But this instead of making thing better, making things appear more worst. As in this the performance degrade due to bottleneck and congestion, basically because of shrinking geometry. If the traditional bus topology is considered, it doesn't prove to be a good alternative due to less scalability provided in this, lack of parallelism, high latency involved, low throughput and more energy consumption along with high power dissipation. For providing the best solution to the existing system-onchip NoC proves to be the best solution. In NoC higher scalability is provided along with the concurrency of execution of multiple tasks by processors working concurrently. And hence Network-on-chip can be considered as a solution to all the problems being faced in the Systemon-chip architecture, and these problems are treated at nano scale level in Networks-on-chip [1, 2, 3, 4]. In last few years a large number of changes has taken place in the Networks-on-chip architecture such as mesh topology, torus, fat tree, etc and also on other application specific architectures [5, 6, 7, 8, 9, 10, 11, 12].

But instead of providing so many solutions over the system-on-chip architecture, networkson-chip still is not a perfect alternative due to some limitations being faced by networks-onchip. The limitations faced by networks-on-chip are high power consumption, large amount of communication cost, and a lower throughput. To deal with these problems a new concept of 3D networks-on-chip architecture came into existence, with low power consumption along with higher speed.

Figure 1.1: Shared Bus Architecture

According to Moore's law the number of transistors are increasing day by day, so to accommodate such a large number of transistors on a single chip, it is required to shrink the geometry of the chip while performance should not be effected negatively. Due to scalability SoC can grow more and more continuously, due to this there is occurrence of many problems such as power dissipation, latency, overheat, management of resources, etc[13, 14]. Interconnection network if considered perform an important role in the performance and power consumption of the chip[15]. Now due to so many problems faced in traditional topologies such as scalability issues and lack of parallelism and concurrency, bus topology and P2P architecture are of no use today[13, 16]. The scalable and parallel connections provided, NoC basically provides an connection between the processors, memory and also provides a facility of custom design. NoC basically provides hop-by-hop communication with the help of the packet switching. Fig.1.1(a) and Fig.1.1(b) show one of the most well-known architectures which are respectively Point-to-Point (P2P) and shared bus systems. As shown in Fig.1.2, NoC architecture connects switch and wires, hence it makes use of the combination of the traditionally build bus and point to point architecture, providing advantages of bot and hence reducing the disadvantages. The basic disadvantages removed using network on chip are large number of long wires as in case of P2P architecture and scalability issues as occurred in shared bus architecture.

### 1.1 Why 3D NoCs?

As the development in the technology the future applications are becoming complex day by day. Due to their complexity they are demanding for the more bandwidth for transaction between memories and cores or for providing communication between the cores of the chip. These

Figure 1.2: Point to Point Architecture

Figure 1.3: Networks on Chip Architecture

factors lead to 2D NoC failure and hence the future is based on the more scalable NoCs such they are so large that they can accommodate hundreds of cores. 2D NoC faces a high dimension of problems hence an introduction to the 3D NoC has proved to be the best alternative for all problems. 2D NoC could not support high diameter but it can easily be supported by the 3D NoC [17, 18]. Diameter can be defined as the number of hops that a flit, packet or message takes for being transferred from source to the destination. If large distance is covered by the flit to traverse from the source to the destination, the latency due to communication will be very high, due to which throughput is very low. The best solution to this problem is that instead of using 2D NoC topology switch to the 3D NoC architecture. Since there is a third dimension in 3D NoC architecture so the density of 3D is much higher than as compared to the 2D NoC topology architecture. Due to the reduced number of wiring the lower interconnection power is required. The reduction in power is basically due to the reduction in the number of hops, as the flit has to cover a lesser number of hops to reach from source to the destination. Due to less hops lesser amount of buffer access is required along with less switch arbitration and less number of interconnection links leading to less traversal. The results of these factors will lead to the decreases in power consumption.

### **1.2** Flit size or Phit Size

- Flit: It is the smaller unit being extracted from information at the link layer, and the information consists of one or several words. There are several types of flit, and it requires several cycles to exchange flits [19, 20].

- **Phit:** At the physical layer the smallest unit of information is basically known as phit, which requires one cycle for transferring of flit over physical layer. Fig.1.3 shows how message is divided into packet which are further split into flit which is a combination of much smaller units called phit [19, 20].

Figure 1.4: Phit and Flit

### **1.3 Routing**

#### **1.3.1 Distributed Routing**

For passing the traffic over the network between routers and nodes there is a requirement of some kind of a routing algorithm which can decide the path followed by the packet or flit to pass from source to the destination [21, 22, 23, 24]. Header associated with packet just contains the address of the destination node. Each router have the information about the address of the neighboring routers. When packet reach to some intermediate router then it is passed to the other router whose address is there in the table of the intermediate router. Passing from router to router and following the path according to the routing table, message is passed from source node to the destination node. If we talk about this routing approach, then it is most favorable in the symmetric and regular topologies, because of the reason that all the routers use same routing algorithm.

#### **1.3.2** Source Routing

In this routing algorithm source node will calculate the full routing path to the destination in advance [21, 22, 23, 24]. This path is pre-calculated by the source node even before injecting the packet in the network. Now since the path is pre-calculated so it will be embedded with the header and hence all the routers in the path will just read the header and will calculate the path to reach the destination. So this technique instead of calculating the routing path at each node

5

partially, the full path is determined and is send along with the packet in the header.

#### 1.3.3 Hybrid Routing

This routing algorithm can be considered as the combination of the distributed and source routing algorithms. In this instead of calculating the full path from the source node to the destination, only the path to some of the intermediate nodes is pre-calculated. Then with the help of these intermediate paths and the paths from the routing table of each node the precise path between the routers are calculated to reach the destination node. As full path is not calculated at once, and the path is calculated in distributed manner and hence it is called distributed routing algorithm.

#### 1.3.4 Centralized Routing

In this the whole routing algorithm relies on the controller. This controller is responsible basically for determining the path from source to the destination node to pass the packet.

### **1.4 Implementation of Routing Algorithm**

#### **1.4.1** Deterministic routing algorithms

In this routing algorithm there would be a routing path which is dedicated and will be used to pass the packet from source to the destination [25, 26]. Every time the packet has to follow the same path between the source and the destination and hence a dedicated path is allotted for transferring packet from source to the destination. It is most simple as only one dedicated path has to be determined for routing packets, and hence faster too as not much calculations required.

#### **1.4.2** Oblivious routing algorithms

In this routing algorithm the determination of the routing path between the two nodes is basic concern and what is happening all around is not need to be considered. S in this routing algorithm no extra information is required to be maintained. So here only the address of the node is considered and other details are of no use. So the information such as the congestion details are not maintained here. Due to this traffic problems such as congestion cannot be resolved.

#### **1.4.3** Adaptive routing algorithms

In this basic concentration is on the avoidance of the congestion. For reducing congestion, in this algorithm the full information about the network traffic is concerned [27, 28]. This information include the details such as network traffic, channel status, faulty regions etc. This technique can be applied and best suitable for the conditions where the traffic status is constant and doesn't change too fast or very frequently. If the traffic pattern change too frequently then it would be costlier to monitor them. Here the network congestion on every intermediate node is calculated.During the occurrence of congestion alternate path are followed which will provide better throughput and lower latency. But here the problem of message arrival out of order can be faced very frequently.

### 1.5 Switching

#### **1.5.1** Circuit Switching

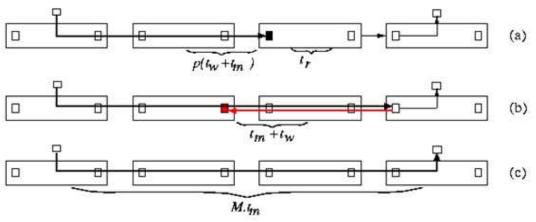

This is the switching algorithm which is basically consisting of two phases which include the circuit establishment phase and the message transmission phase. There is a probe message which will go towards destination node, via a reserved physical links [23, 29, 30]. These physical links are reserved as the probe passes through the intermediate routers (see Fig.1.4(a)). Once the probe has reached to the destination the full path is set up. After the establishment of the path a flit is sent back over this path to acknowledge that the path between source and destination are set. When the acknowledgment is received on the sender's side then the sender is capable of transmitting complete message at the full bandwidth. The path forms a dedicated circuit that is reserved for full time till message transmission take place (see Fig.1.4(c)).

Figure 1.5: Circuit Switching

#### 1.5.2 Store-and-forward (SF) switching or Packet Switching

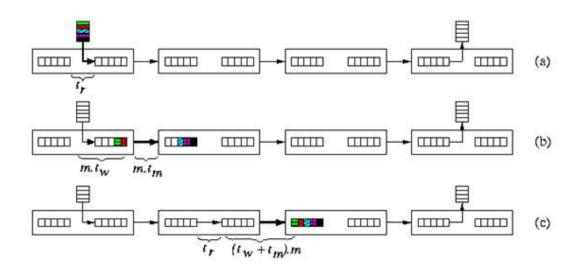

Here in this algorithm the message is split into different fixed length packets. These packets consist of flits, along with the header flit [23, 31, 32]. There are input and output buffers for each distinct packet over the network channel. From source to the destination every packet is treated as an unique identity and hence routed individually. The steps termed in the stop and forward switching is called a hop. In this the packet is copied from the output buffer of one node to the input buffer of the other node. Once the full packet is buffered in the input buffer of the node is responsible for further routing decision. In Fig.1.5 Store-and-forward switching of a packet is shown. Fig.1.5(a) Routing decision for the first router is being considered. Fig.1.5(b) shows the packet taking the first hop, after being copied to output buffer, to the second router. Fig.1.5(c) shows the structure and conditions of the whole packet after occurrence of the second hop.

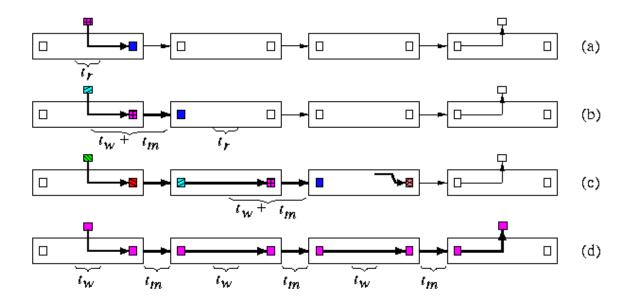

#### 1.5.3 Virtual cut-through (VCT) switching

This technique is the most costlier techniques over the other techniques discussed till now. Like in store and forward here also the message is broken down into packets and there buffers present in each router to store these packets [23, 33]. Header flit will be removed from the packet at the next router as instant as the routing decision is taken, conditioned output channel should be free. Whenever the new flit reaches the router it is being buffered. And it is further passed to the immediate neighboring router if the output channel is free. If the packet cannot be further

8

Figure 1.6: Store-and-forward (SF) switching or Packet Switching

processed then it will keep on waiting in the current router for its chance to come, till the other flits not releasing the channels occupied by them. But if the channel is free and there is no congestion then the packet will be divided into flits and these flits will pass over the channel in the continuous flow. Till then all the other buffers in the routing path are blocked to take over more packets. In Fig.1.6 Virtual cut-through switching of a packet. Fig.1.6(a) shows the moving of the header flit to the output buffer of the first packet. Fig.1.6(b) shows the distribution of the header over the second router whereas the subsequent flits will continue to follow their paths. Fig.1.6(c) shows that even after pulling the flits in a chain the header is cut through, and its output buffer is reserved for further communication. Fig.1.6(d) gives details that how the chained packets are contracted to form the message again and then the packet will be buffered in the first router. While doing this all the previously allocated links will be released. Fig.1.6(e) shows the pipe-lining of the flits for moving towards the destination node.

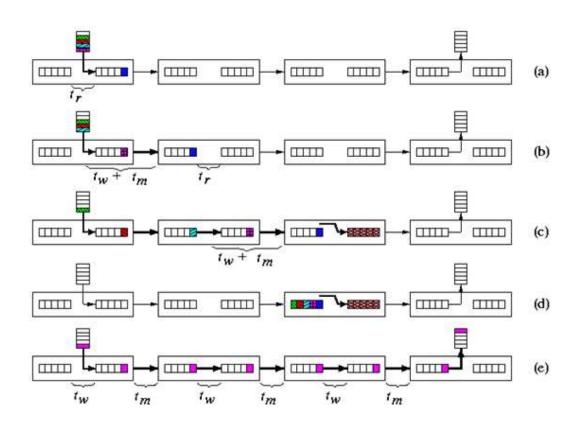

#### **1.5.4** Wormhole (WH) switching

Like conflict-free virtual circuit switching, the packets are split into flits and are pipelines then passed over the route. In this algorithm also different packets cannot be interleaved or multiplexed on the channel without providing it an additional support for architecture [23, 34, 35]. The major difference between the two techniques is that in this there is no concept of buffers for the packets. Still there is a provision of buffers and here every router has a small size of buffer to store one or a very few number of flits. Header flit builds or initialize a path from source to

Figure 1.7: Virtual cut-through switching

Figure 1.8: Wormhole switching

the destination which is being followed from source to the destination node in a pipeline manner. Here in this a wormhole is formed by the sequence of the buffers and the links. Number of flits in the packet determine the length of the path as they are directly proportional to each other. Whole path is being traversed between the source and the destination. If the channel has congestion due to traffic and the header cannot be processed due to the busy output channel, the whole chain of flits will get stalled. To resolve this issue the flits should occupy the buffers in the routers blocking the other type of communication taking place. Conflict-free communication latency  $t_{WH}$  produces same results as in case of the VCT switching. Due to this it is proportional to the summation including the path length and size of the packet. In Fig.1.7 explanation of how wormhole switching of a packet works is given in a diagrammatic context. Fig.1.7(a) shows the copying of the header to the output buffer once the routing decision is taken. Fig.1.7(b) shows the transferring of the header flit to the second router along with the other flits following it. Fig.1.7(c) When the header flit is arrived into a router whose output channel is busy, whole flits in the path will get stalled, and all channels will be blocked. Fig.1.7(d) shows that how the flits are pipelined in the case of the conflict-free routing algorithm by the establishment of the wormhole switching across the routers.

## **1.6 Router Architectures**

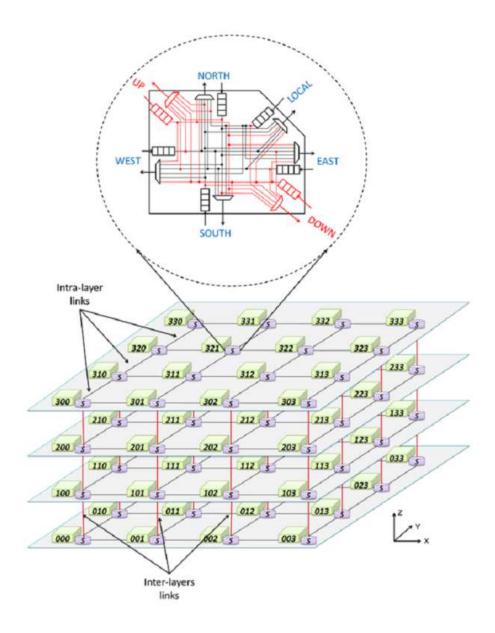

Traditionally used 7X7 3D router which was based on the shared bus architecture for communication interface between different layers are modified and an introduction to the 3D NoC bus based hybrid topology [36, 37, 38, 39, 40, 41]. Due to this the number of ports are reduced from 7 to 6, but still there is an issue as the flits passing from one layer to other has to fight for accessing the shared bus, as it is only responsible for the communication between the layers. High traffic and network congestion will lead to an undesirable performance of the system. If we talk about the 2D router architecture then there are 5 ports which include NORTH, SOUTH, EAST, WEST, LOCAL. If the 3D router architecture is considered then there are 7 ports among which 5 ports are same as mentioned above with two extra ports UP and DOWN ports as shown in Fig. 1.8. From the figure it is clearly visible that inter-layer channels are used to provide linking between the inter-layer channel. But the switches used in different layers are connected to each other using intra-layer links. And each router or switch is connected to a single processing element.

Figure 1.9: Router Architecture

## Chapter 2

## **Literature Review**

### 2.1 Research Papers

In this section the basic idea is to give the explanation of some of the papers which are being reviewed by me for reference to generate new topology.

#### 2.1.1 Key Research Problems in NoC Design: A Holistic Perspective

In this paper they have defined a 3D design space that involves issues related to communication infrastructure synthesis, communication paradigm selection and application mapping optimization. In the paper to give an explanation about the application and architecture description some of the graphs are considered which include communication task graph and application characterization graph. In the paper eight problem domains are discussed [42]. These problems include:

- Topology Synthesis Problem

- Channel Width Problem

- Buffer Sizing Problem

- Floorplanning Problem

14

- Routing Problem

- Switching Problem

- Scheduling Problem

- IP Mapping Problem

The main purpose to read the paper is to get through an idea that what are the fields in which improvement is required. After going through the problems defined in this paper and having read about all these problems i am able to decide what to choose as a problem domain for research work.

### 2.1.2 3D Network-on-Chip Architectures Using Homogeneous Meshes and Heterogeneous Floorplans [43]

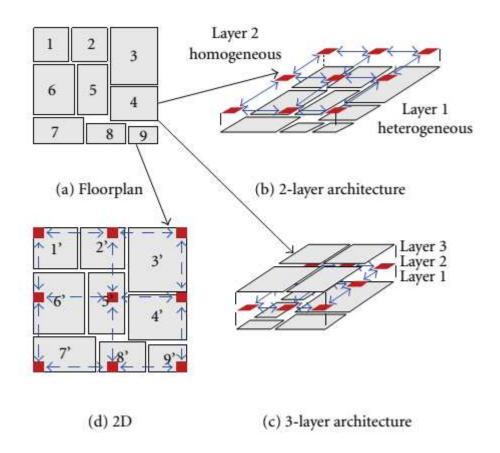

In this paper, they have proposed a new 3D architectures for networks-on-chip which are of the form either 2-layer or 3-layer. For these layers a homogeneous regular mesh topology is used along with some of the heterogeneous topologies for the floorplanning layers. The advantages of heterogeneous floorplans and regular mesh networks are combined and the results obtained are compared here in this paper.

In Fig.2.1(a) initial floorplan with no router is shown while Fig.2.1(b) shows two layer architecture, Fig.2.1(c) shows 3 layer architecture and Fig.2.1(d) shows the 2D implementation for each IP/core for calculation of the area which is required in the interfaces of the network, routers along with the wires used for the physical links.

Two NoC architectures are proposed in the paper which include 3D NoC architectures for 2layer along with the 3-layer architectures. This architecture make use of the homogeneous network on a different layer and that of the heterogeneous floorplans on the different layers. So for the purpose of attaining flexibility and predicting delay the IP/cores can have an arbitrary size. Designing difficulties are resolved in this approach because of the irregularities in size of IP/core that are basically being addressed by some of the specialized algorithms for routing. Author in this paper has proposed the software framework which is versatile in nature for investigating the advantages of the proposed architectures for 3D NoC. In this the integration of the efficient  $B^*$  Tree-based floorplanner with a NoC simulator which is cycle-accurate for maximum performance is used in the results obtained by experiments.

Figure 2.1: Floorplans showing the combined use of homogeneous floorplan and heterogeneous floorplans.

This paper has proposed that due to the shrinking of the geometries of circuits the on-chip interconnection networks have become the most prominent for the performance bottleneck. As more functionality is integrated into a single chip, interconnection requirements become complex. Customization aims at satisfying operating speed requirements while meeting the power budget. This is achieved if one can put the interconnections which are very critical as short as possible with the help of partitioning of the system placement of the block in the layout. According to the paper minimization of global communication traffic is concentrated, along with cost and design space. Heavily communicating task should be mapped to the same PE. As shorter the path low is the delay and less power consumption. This paper has also proposed that an Iterative approach should be followed during the development of topologies for 3D NoC. If design fails to meet the particular specification at any point then previous stage is resumed [44].

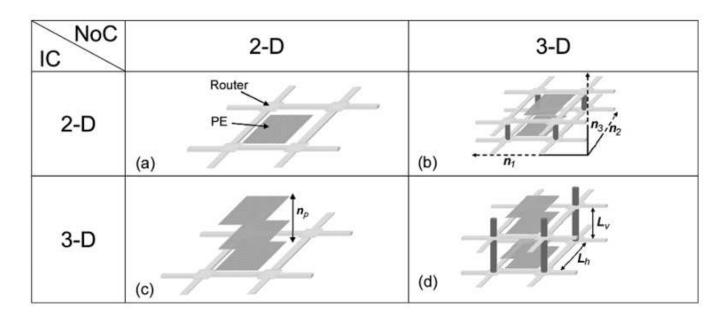

#### 2.1.4 3-D Topologies for Networks-on-Chip [45]

In this paper the author has concentrated upon the those planes which has the property to be stacked vertically and there exist some of the symmetry between the horizontal and vertical communication channels of the network, as the basis for speed and power consumption in the models. This paper has also considered diversity occurring among the number of nodes that is being utilized in the 3D, which reduces the average number of hops traversed by a packet. In this paper it is mentioned that NoC offers high flexibility and also the structure of the network is regular, which is capable of supporting an interconnect models which is simple and can handle a large amount of fault tolerance. The canonical interconnect backbone of the network combined with appropriate communication protocols enhance the flexibility of such systems. They have considered Multidimensional interconnection networks, and these networks are analyzed for multiple constraints, which include a constant bisection-width and the other parameter as pinout constraints. NoC has no similarity with the generic interconnection networks and there lies a great difference between the two. This paper puts a great emphasis on the Optimization of the topology and also minimize the zero-load latency and plays an important role in the optimization of power consumption in a network. The optimization of topologies greatly depends on the number of parameters used to characterize the router and the channel for communication, for example the number of ports involved in the router, the communication channel length, and the other characteristics or properties of the interconnection networks such as impedance. Fig.2.2 shows the various NoC topologies which include (a) 2-D IC-2-D NoC (b) 2-D IC-3-D NoC (c)

18

Figure 2.2: Various NoC Topologies

3-D IC-2-D NoC (d) 3-D IC-3-D NoC.

### 2.1.5 Energy and Latency Evaluation of NoC Topologies [46]

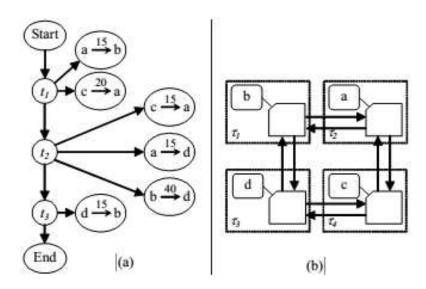

This paper concentrates on finding the topology, among regular and irregular NoC topologies, that better fits the application requirements. SUNMAP, this tool selects best topology for given application and generates mapping of core onto that topology. This paper has justified that fat-tree topology is a strongly fulfills the latency constraints for many applications, while mesh topology achieves less energy consumption. In this paper mapping applications onto different networks-on-chip (NoCs) topologies is done such that the mapping of the cores on to the ports of routers, one should consider the requirements such as the latency involved and energy consumption. This paper include two graphs are being used and they include ACP (Application Communication Pattern) graph, CRG (Communication Resource Graph) and CTG ( Communication Task Graph).

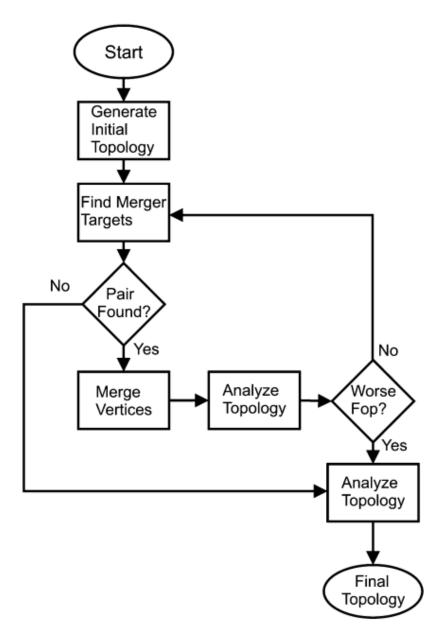

For each message in the application, it is a necessity to find out a path between the vertexes of CRG which involve sender and the receiver. In order to verify that the bandwidth required by the paths must be similar to the one which is necessary for the application. So in Fig.2.3 ACP and CRG relation ate shown diagrammatically.

18

Figure 2.3: ACP and CRG

## 2.1.6 Throughput-Oriented NoC Topology Generation and Analysis for High Performance SoCs [47]

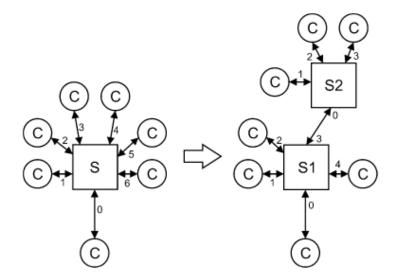

Predictive analysis for estimation of degree of contention is the basic idea of researcher in this paper, instead of performing detailed simulation. This paper has justified that irregular topologies can also provide better performance if correctly built. In this paper packet-switching is considered as an extension of wormhole switching. Topology generation mechanism is carried out in this by using two techniques Switch Merger Technique and switch Partitioning Technique. In Fig.2.4 the switches which have larger number of nodes attached to them and participate in communication to each other the maximum number of times are merged to each other to form a single switch. This merging technique causes the less delay in communication and hence energy and cost are saved as heavily communicating nodes are at the same switch. In Fig.2.5 Suppose a switch has too many number of nodes attached to it is broken into two parts causing the traffic to be distributed over multiple switches and hence controlling congestion. Fig.2.6 shows an algorithmic representation of creating a new topology using iterative approach which is proposed in this paper.

Figure 2.4: Example of switch merger.

Figure 2.5: Example of switch partitioning process.

Figure 2.6: Topology generation Algorithm.

# **Chapter 3**

# **Problem Statement**

For reduction of design space, communication delay and cost involved, NoC tries to reduce the number of connections. Reduction in the number of communication channels leads to lack in functionality during traffic and noise. Lesser number of channels between any two nodes leads to the situation of bottleneck, due to which performance is also reduced. So the main concern of this research is to reduce the end to end delay, packet latency, network latency and link utilization, keeping area and bandwidth constant. For this purpose, the comparative studies of all the existing NoC topology is done and then providing a new topology which will be better in every perspective, than the already existing one's, in terms of QoS parameters.

#### **3.1 Problem Formulation**

Given: A core communication graph G (or G).

Find: The topology generated should optimize O(A,G), subject to the constraints specified by Const(A,G).

- O(A,G) can be a metric for reliability and performance of the network, such as end-to-end latency, network latency, packet network latency, loss probability, link utilization etc.

- Const(A,G) can be considered as the amount of needed resources (e.g. area, wiring, etc.), cost and bandwidth imposed by the application.

# **Chapter 4**

## **Proposed Approach**

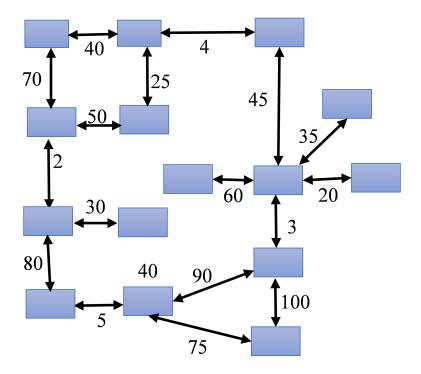

First of all, determine the cores having the maximum amount of communication among themselves. Communication among the cores can be determined on the basis of communication task graph. In this graph the cores are considered as the vertices and the links between them determines the communication between the cores. Links are assigned some weights and these weights determines how much communication is there among the cores. Links having maximum weights determine the cores having maximum communication whereas the links having minimum weights determines the cores having least amount of communication. Cores with maximum communication should be in the same cluster so that they take least time for communication, and hence speed up the process. Core communicating lesser amount of times can be in different clusters because if time taken by these cores is more, even then much difference doesn't occur. Here for the simplicity we consider the router and its corresponding core as a node. Among the nodes within a clusters one or more nodes are chosen as the master node. Master node act as an intermediate between the two clusters. It is the node responsible for the inter-core communication. The clusters here can have any of the NoC topology as per the communication requirements among the cores within the cluster. Since single cluster can communicate to the multiple clusters so there can be more than one master node within the cluster. Here if we consider the amount of traffic then the maximum traffic is found to be at the links joining the two master nodes. As this is the single links which is responsible for the inter cluster communication. To reduce the amount of traffic on these links, it is required that some special configuration of these links are required. Configuration of the links means the delay, bandwidth and the type of wire used in the links. In these links varying the bandwidth of the links have made it possible to simulate the required communication among the cores.

#### 4.1 Cluster Formation

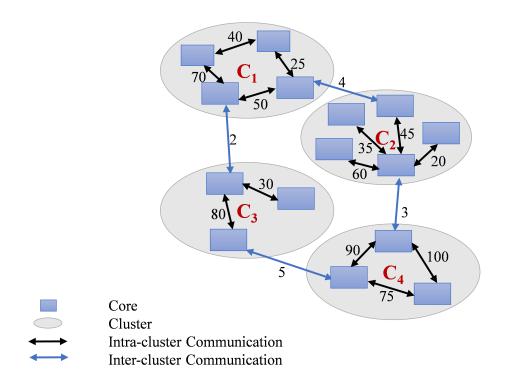

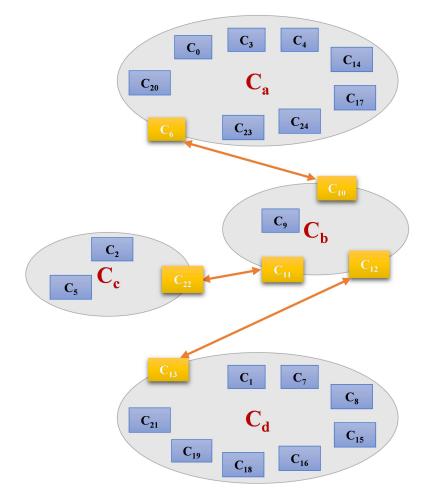

Cluster in CBCT is formed using the communication based cluster graph (CBCG). CBCG is a directed connected graph which can be represented as  $CBCG = (C, I_l)$  where, C represents the clusters and  $I_l$  represents the inter-cluster links. In CBCG, the clusters of most communicating cores are formed, the corresponding routers attached to the cores are also considered in the same cluster. Fig.4.1 gives the communication between the cores. The weight of edges describe the amount of communication taking place between the two cores. More the edge weight, more is the communication. According to the amount of communication clusters can be defined, and communication based cluster graph is obtained. The clusters are shown in the Fig.4.2 as  $C_1, C_2, C_3, C_4$  and the links inside each cluster represents the communication between the cores in the cluster. In Fig.4.2, the values associated with the links represent the communication between the cores. These links between the cores of the cluster are caller intra-cluster links and the links through which the clusters are connected together are called the inter-cluster links. Cores of two distinct clusters have minimum communication between them. The cores in the CBCG as shown in Fig.4.2 can be connected to each other using any topology within a single cluster such that most communicating cores lie within same cluster. Algorithm 1 gives the details for the formation of cluster. In the algorithm 1, 'N' gives the total number of cores present,  $T_h$  defines the threshold that how many clusters to be formed, and array V stores the details of the cores, already visited during the formation of clusters.

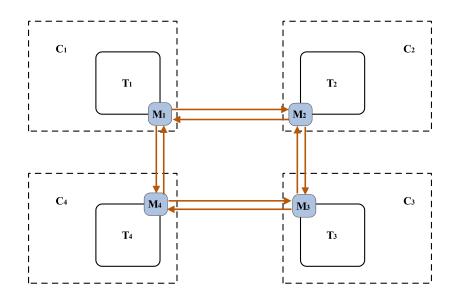

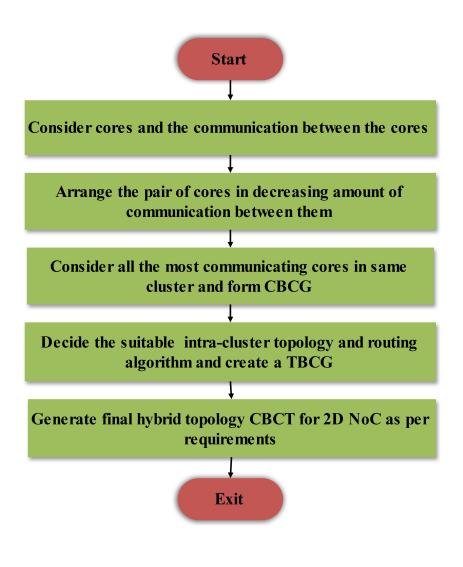

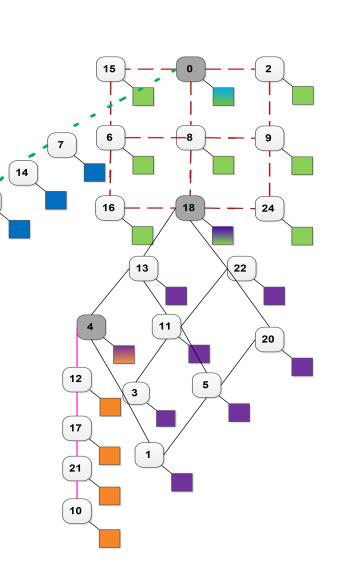

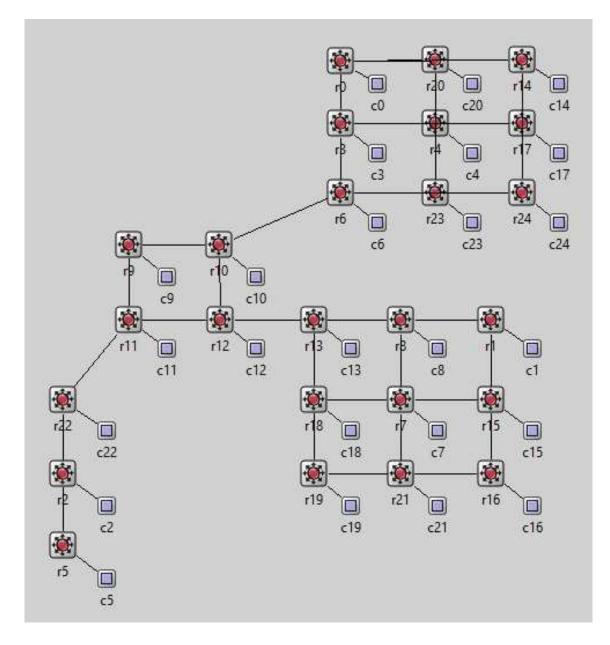

CBCG graph can further be reduced in more generalized graph TBCG.  $TBCG = \langle T, t \rangle$  where, T represents the topology used to arrange the cores within the cluster and t represents the topology used to connect these clusters. In TBCG as shown in Fig.4.3,  $T_i$  represents the topology in cluster  $C_i$  and  $M_i$  represents the master router for each cluster. Master router is responsible for the inter-cluster communication. From each cluster, a master router is chosen such that it provides connectivity to the outside world i.e. other clusters. The topologies used within the cluster can vary for each cluster depending upon the requirements. We are dealing with heterogeneous networks, so for proposed approach, we have considered different topology, but any other topology such as star, bus etc. can also be used to connect the different clusters. Flowchart shown in Fig.4.4 describe the steps to be followed for the creation of the CBCT topology.

Algorithm 1: Cluster formation for CBCG graph **Data**: N = number of cores,  $\{1, ..., n\}$ ,  $T_h$  = maximum possible clusters, V[N] = visited cores, j=0, i=0; Result: Cluster formation while  $(j! = T_h)$  do if i = = 0 then while size of(V)! = N do Let (x,y) be highest cost edge from E; if  $((x \in V) \& \& (y \in V))$  then E - (x,y);Continue; else if  $x \in V$  then Assign core y to the cluster to which x belongs; E - (x,y);else if  $y \in V$  then Assign core x to the cluster to which y belongs; E - (x,y);else Assign both cores x and y to new cluster  $C_i$ ; E - (x,y);i++; Put cores x and y in V whichever is not present in V; else if  $j < T_h$  then Take edge (x,y) having least cost where  $x, y \in C_i$ ; Assign both cores x and y to new cluster  $C_i$ ; i++; else if  $j > T_h$  then Take edge (x,y) having highest cost where  $x \in C_i$  and  $y \in C_j$ ; Merge the clusters  $C_i$  and  $C_j$ ; i–; j=i;

Figure 4.1: Communication between Cores

#### 4.2 Structure of Router and Core for implementation of CBCT

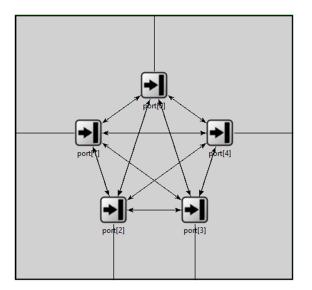

Router, used to implement proposed approach CBCT, is a 2D router which consists of 5 inports and 5 out-ports. In-ports are used by node (router and core) to receive the packet whereas, out-port is used to send the packets to destination. There are 4 ports which are referenced as northPort, southPort, eastPort, westPort to communicate with the routers being connected in the north, south, east and west direction respectively. Along with these ports, there is one more port i.e. corePort. This port provides the connectivity among the router and the core. Fig.4.5 gives the diagrammatic representation of the 2D router being used in the CBCT approach. In Fig.4.5, port[0], port[2], port[4], port[1] represents the northPort, southPort, eastPort, westPort respectively, and port[3] represents corePort. Direction of arrow shows the flow of packets and communication among connected routers. If the structure of the core is considered, then for the implementation of the CBCT, the core is considered as source as well as the sink as shown in Fig.4.6. The two cores involved in the communication act as source and the sink. Core which transmit the packet to other core act as the source, whereas the core receiving the packets is referred as the sink.

Figure 4.2: Intra-cluster and inter-cluster communication in CBCT

Figure 4.3: Topology based cluster graph

Figure 4.4: Flowchart for generating CBCT topology

Figure 4.5: Structure of 2D router used for CBCT

Figure 4.6: Structure of 2D core used for CBCT

### 4.3 Master based Routing Algorithm

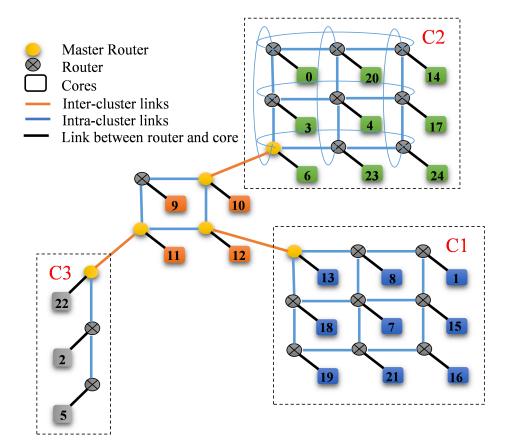

Existing routing algorithms doesn't prove to be an optimized solution for the implementation of the proposed approach, so we have introduced a routing algorithm i.e. master based routing algorithm. In master based routing algorithm, the routers which are the intermediate between two cluster topologies act as the master routers. As shown in the Fig.4.9 yellow colored routers are the master routers as they are intermediates and they are responsible for the communication between the clusters. These clusters are the networks, which consists of the most communicating components within same cluster, and lesser communicating in different cluster. As shown in the Fig.4.9, considers that there are 3 different topologies used in the 3 different clusters. Cluster  $C_1$  consists of mesh topology, cluster  $C_2$  consist of torus topology and cluster  $C_3$  uses bus topology for connecting different components for communication. For the purpose of routing the packets from source to destination, suitable routing algorithm corresponding to the topology is used like XY routing is best suited to mesh topology, if both source and destination belongs to same cluster, whereas if the source and destination belong to different clusters, then master based routing algorithm comes into active state. In master based routing algorithm, master has all the information of the routers and their corresponding cores belonging to the same cluster. Master also keeps record of the other master router directly or indirectly attached to it. Routers, other than master, also have the record to which cluster that router belongs to and have the information about their master. Suppose source and destination belongs to different clusters, then the packet is passed from the source to the master (corresponding to that cluster to which the source belongs). The master will communicate the other masters for checking to which cluster the destination core belongs to, then it will pass the packet to that master either directly or indirectly. Upon reaching to the master of destination core (following the corresponding routing algorithm associated with the topology of cluster), packet will route to the destination core.

#### 4.4 CBCT : Communication based Cluster Topology

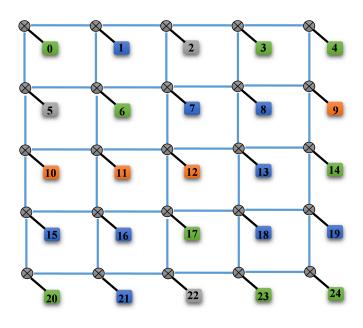

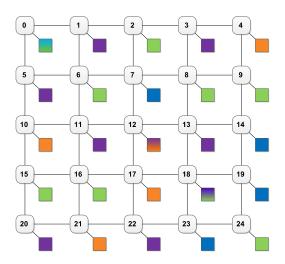

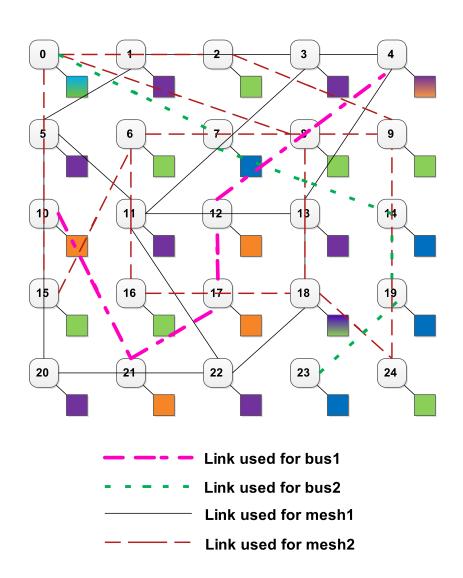

In order to evaluate the performance of CBCT topology, we compared the result of CBCT topology with mesh topology. We have considered 5X5 2D mesh topology as shown in Fig.4.7, in which the most communicating cores are represented by same colored cubes. Routers are represented as gray colored circles with cross.

For simulation of CBCT, we have considered a CBCG as shown in Fig.4.8. In Fig.4.8,

#### Algorithm 2: Master based routing

Data: Communication based cluster graph (CBCG)

Output: Cluster formation with suitable topology within and between clusters

Initialize  $B_{inter}$  and  $B_{intra}$ ;

Set  $B_{intra} = \text{constant};$

$B_{inter} = \frac{(n_t - n_m) * B_{intra}}{n_m}$ ;

while cores are not assigned to some cluster do

while most communicating cores, belonging to same group in the CBCG, are not all

assigned to some cluster do

Cluster[k] = core[i];

Choose master core from each cluster and Master[i] = core[j];

Assign suitable topology to be used within the clusters and between the clusters according to the requirements;

if both source and destination belong to same cluster then

Pass packet from source to destination directly;

else

Pass the packet to the Master core;

Master core will further pass it to the other master core and in the same way to other

master cores till the cluster having destination core is not reached;

Pass packet successfully to the destination;

there are 4 clusters with most communicating cores in the same cluster. These clusters are represented as  $C_a, C_b, C_c$  and  $C_d$ . Cluster  $C_a$  is a combination of most communicating cores  $< c_0, c_3, c_4, c_6, c_{14}, c_{17}, c_{20}, c_{23}, c_{24} >$ ,  $C_b$  consists of  $< c_9, c_{10}, c_{11}, c_{12} >$ ,  $C_c$  is a collection of cores  $< c_2, c_5, c_{22} >$  and  $C_d$  consists of  $< c_1, c_7, c_8, c_{13}, c_{15}, c_{16}, c_{18}, c_{19}, c_{21} >$ . If Fig.4.7 and Fig.4.9 are considered, we can conclude that the most communicating cores are far away from each other in mesh topology, and hence the hop count is large. For example, in Fig.4.7 cores 0 and 24 are most communicating cores, and the hop count between these cores is 8, so every time for communication between these two cores, it is required to cover a hop count of 8. This causes an increase in latency with an extra overhead. In CBCT as shown in Fig.4.9, the hop count required for the communication between cores 0 and 24 is 4, which is 50% efficient than the existing torus topology. Using CBCT approach, generated clustered topology can provide 40% to 80% of efficiency over existing topologies. Fig.4.10 shows flowchart for creating CBCT topology and routing packets from source to destination.

If two cores 0 and 1 are considered in Fig.4.7, it is clear that they are least communicating

Figure 4.7: 5X5 2D Mesh Topology

cores represented using different colors, so keeping these cores far away will not affect the performance, hence in CBCT as shown in Fig.4.9, in order to bring most communicating cores nearby, these less communicating cores can be placed far from each other. To provide better performance, it is required to optimize latency and overhead. In order to place all the most communicating cores in one cluster, it should be verified that the hop count between these cores of the cluster should not increase as compared to the hop count between the same cores in mesh topology. The hop count between the two most communicating cores in the mesh topology, is considered as the threshold for this pair of cores in the CBCT. While designing the CBCT, it is required to consider that the threshold determined for a particular pair of cores should be minimized and hop count should be reduced. In proposed approach, our basic aim is to produce a hybrid topology, which can follow all the QoS requirements such as minimum latency, minimum bandwidth and maximization of the throughput. Communication among the cores can be determined by using CBCG graph with the weights assigned to the links. Cores with maximum communication should be in the same cluster, so that they take less time for communication, and hence improves processing speed. Less communicating cores can be in different clusters. Among the nodes within a clusters, one or more nodes are chosen as the master node. Master node act as an intermediate between the two clusters. It is the node responsible for the inter-core communication. The clusters can have any of the NoC topology

Figure 4.8: Cluster of most communicating cores

Figure 4.9: Communication based Cluster topology

Figure 4.10: Flowchart for creating CBCT topology and routing packets from source to destination

as per the communication requirements among the cores within the cluster. Since single cluster can communicate to the multiple clusters, so there can be more than one master node within the cluster. If we consider the amount of traffic, then the maximum traffic is found to be at the links joining the two master nodes, as this is the single links which is responsible for the inter cluster communication. To reduce the amount of traffic on these inter-cluster links, it is required that some special configuration of these links have to be specified. Configuration of the links means the delay, bandwidth and the type of wire used as the links. In inter-cluster links, varying the bandwidth of the links have made it possible to simulate the required communication among the cores. For this purpose, the mathematical formula used in the proposed approach to set the bandwidth of the inter-cluster links is given as in Equation 4.1:

$$B_{inter} = \frac{N_{nm} \times B_{intra}}{N_m},\tag{4.1}$$

Where,  $B_{inter}$  is the bandwidth of the inter-cluster links,  $N_{nm}$  is the number of non-master cores,  $B_{intra}$  is the bandwidth of intra-cluster links and  $N_m$  is number of master cores. This bandwidth reduces the traffic as huge amount of bandwidth is allocated to the most congested links. Depending upon the source and sink, the path is determined in the topology and packets are routed from source to destination using Master-based routing algorithm as discussed in section 4.3.

#### 4.5 3D CBCT topologies for NoC

In this section the details about the implementation and designing of the CBCT for 3D NoC are discussed. For the purpose of comparing the results of the proposed 3D NoC CBCT topology we have implemented 3D NoC Mesh topology in OMNET++. The configuration of 3D Mesh topology is 5 X 5 X 4. In this mesh topology there are 4 layers each having dimension 4 X 4, i.e., there are 25 cores in each layer. In case of 3D CBCT for NoC we have considered two of the architectures, (i) with most communicating cores on different layers, (ii) most communicating cores on the same layer. In the first case as the most communicating cores are at different layers of mesh topology and hence a lot of time and effort are wasted for them to communicate to each other. But in CBCT the cluster for these most communicating cores are formed and hence the overhead involved in the mesh topology is reduced to a great extent.

Based on the single case we cannot prove that CBCT will produce best results for all the combinations possible. Hence to prove it best in all the cases we have considered the best case of

Figure 4.11: 5X5 2D Mesh Topology

the mesh topology. In the best case all the most communicating cores will reside on the same layer of the mesh topology. So for the CBCT the clusters of the cores on the same layer are formed. While considering the mesh topology in its best case also it was concluded from the experimental results that CBCT for 3D NoC proves to be the best.

Now the main focus is to make the CBCT topology geometrically equivalent to orignal mesh topology. For this first take the mesh topology. Determine the most communicating cores and create the CBCG. Then determine the topology for each cluster using TBCG. Add the links between the most communicating cores and remove the links in between the less communicating or non-communicating cores. Fig. 4.11 shows the given mesh topology. Fig. 4.11 shows the initially provided 5X5 mesh topology. Determine the most communicating cores in the given mesh topology. The most communicating cores have same color for differentiation. Some cores in the Fig. 4.11 has two colors, it determines that it is common to two of the clusters.Fig. 4.12 shows the formation of the clusters and generation of the heterogeneous and hybrid clustered topology. Fig. 4.13 shows that the mesh topology shown in Fig. 4.11 and CBCT shown in Fig. 4.12 are logically equivalent in terms of geometry, and hence the CBCT topology will consume nearly equivalent area as taken by mesh topology.

Figure 4.12: Heterogeneous and hybrid Clustered topology

Figure 4.13: Clustered topology geometrically equivalent to mesh topology

#### 4.6 Quality of Services

For the NoC topology in the proposed approach, we have multiple communication based clusters. QoS in CBCT topology can be determined by the contribution of the QoS parameters of each cluster individually. We consider the clusters as  $\langle C_1, C_2, ..., C_n \rangle$ , for each cluster a set of QoS parameters will be defined based on the inter cluster or local topology used in that cluster. Let us consider the QoS parameters as  $\langle Q_{i1}, Q_{i2}, ..., Q_{in} \rangle$  where, *i* denotes the cluster number. These QoS parameters considered can be normalized to give a threshold value by averaging the minimum and maximum QoS value obtained.

$$Q_{i\_min} = \min\{Q_{ij}\} \qquad \qquad Q_{i\_max} = \max\{Q_{ij}\} \qquad (4.2)$$

In Equation 4.2, *i* denotes the cluster number and *j* denotes the particular parameter for that cluster. We have to consider the mean or the average of two values in order to get the  $Q_{th}$  i.e. QoS threshold value for the particular cluster as calculated in Equation 4.3:

$$\overline{Q_{l\_th}} = \frac{\Sigma(Q_{i_{min}}, Q_{i_{max}})}{2}$$

(4.3)

QoS value for all the parameters of the cluster are considered and the average is calculated as in Equation 4.4:

$$\overline{Q}_l = \frac{\sum_{j=1^n Q_{ij}}}{n} \tag{4.4}$$

This average QoS value obtained decides whether the topology developed is best or not. For the experimental results, we have considered that, if  $(\overline{Q_l}) < (\overline{Q_{l \perp h}})$ , then the topology generated is not fully optimized but if  $(\overline{Q_l}) > (\overline{Q_{l \perp h}})$ , then the topology generated is most optimized. For obtaining a fully optimize global topology, we have introduced the concept of priorities. The parameter which provides  $Q_{i\_max}$  is considered to be at highest priority and the parameter which provides  $Q_{i\_min}$  is at lowest priority. So the QoS values at the local level, i.e. for each cluster is considered as given in Equation 4.5:

$$Q_i = P_{i1} * Q_{i1} + P_{i2} * Q_{i2} + \ldots + P_{in} * Q_{in}$$

(4.5)

Where,  $P_{ij}$  determines the priority decided for  $i^{th}$  cluster and  $j^{th}$  QoS parameter for that