## JAYPEE UNIVERSITY OF INFORMATION TECHNOLOGY, WAKNAGHAT TEST -1 EXAMINATION- 2025

## M. Tech.-II Semester (CSE/IT/ECE/CE/BT/BI)

COURSE CODE (CREDITS): 21M1WEC239 (3)

MAX. MARKS: 15

COURSE NAME: CMOS DIGITAL DESIGN TECHNIQUES

COURSE INSTRUCTORS: Dr. HARSH SOHAL

MAX. TIME: 1 Hour

Note: (a) All questions are compulsory.

(b) The candidate is allowed to make Suitable numeric assumptions wherever required for solving problems

| Q.            | Question                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CO  | Marks |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| <b>No.</b> Q1 | <ul> <li>(a) Describe the following with respect to VLSI circuits with example: [0.5×4=2]</li> <li>(i) Moore's Law</li> <li>(ii) Inversion layer</li> <li>(iii) Feature size</li> <li>(iv) Cross talk</li> <li>(b) What is noise margin? Why is it important to have a higher noise margin in digital CMOS circuits? For a given inverter the V<sub>OH</sub>=1.9V; V<sub>OL</sub>= 0.2V; V<sub>IL</sub> = 0.4V; V<sub>IH</sub>=1.7V. Calculate Noise</li> </ul> | COI | 4     |

| Q2            | Margins, NM <sub>L</sub> and NM <sub>H</sub> . [2]  (a) Explain various Fundamental Design Metrics in CMOS Digital Design [2]                                                                                                                                                                                                                                                                                                                                   | CO2 | 2     |

| Q3            | (a) You are given a wafer of the size of 30 cm, die size of 2.5 cm <sup>2</sup> , with 1 defects/cm <sup>2</sup> ; α (the measure of manufacturing process complexity) =3. Cost of the wafer is INR 200,000. Calculate: (i) dies per wafer (ii) die yield (iii) cost of one die. [1+1+2]                                                                                                                                                                        | CO2 | 4     |

| Q4            | What are the oxide capacitances with respect to n-MOSFET? Explain the total oxide capacitance in cut off region, Linear region, saturation region operation of an nMOSFET with the help of suitable diagrams while giving final mathematical equations for all oxide capacitances.                                                                                                                                                                              |     | 4     |

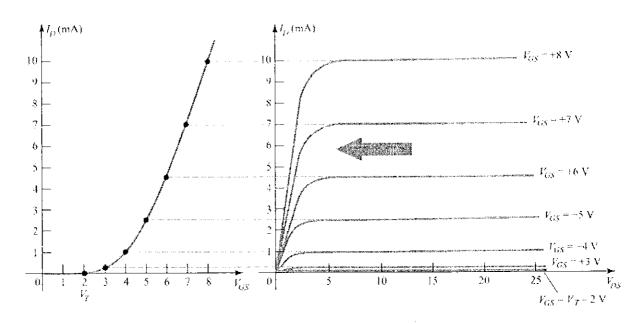

| Q5            | In the Fig. 1. below are the Transfer characteristics of a BJT or an E MOSFET or a D-MOSFET or a JFET? Choose the correct option with explanation. [1]                                                                                                                                                                                                                                                                                                          | CO1 | 1     |

Fig. 1